# PRS-753 Line Protection Instruction Manual

CYG SUNRI CO., LTD.

# **Preface**

#### **User's Guideline**

This instruction manual contains full information of the equipment, including function descriptions, logic diagrams, input signals, output signals, setting parameters and technical parameters. It also lists the operations on safe handling, commissioning and maintaining of this equipment. The instruction manual can be used as a technical reference during the whole product life cycle.

Documentation and manufactured equipment purchased from CYG SUNRI CO., LTD. are dispatched separately due to the necessary manufacturing period. Therefore, they sometimes may not reach the recipients at the same time. Therefore, this manual is provided as a technical reference to commission the equipment.

The installation and commissioning personnel should read all relevant chapters carefully and get a thorough knowledge of the contents of this manual, before conducting any operation to the equipment. In this way, the personnel can get the required knowledge in handling electronic equipment.

This manual contains a security chapter which describes the safety precautions recommended when using the equipment. Before installing and using the equipment, this chapter is recommended to be thoroughly read and understood.

## **Personnel Security**

The content in this chapter specifically describes to prevent and reduce the safety accidents in electric power production and construction procedures, to ensure the personal safety and health of employees in production activities and to ensure the power grids stable operation and reliable power supply.

Any kind of directly touching with the metal parts of the electrical equipment should be avoided when electrical equipment is on operation, because of the potential electric shock risk. Neglecting warning notices should be prevented because the improperly operation may damage the device, even cause personnel injury.

The good operating condition of the equipment depends on proper shipping and handling, proper storage, installation, commissioning and maintenance. Therefore, only qualified personnel should be allowed to operate the equipment. Intended personnel are individuals who:

- Have a thorough knowledge of protection systems, protection equipment, protection functions and the configured functional logic in the IEDs;

- Have a basic knowledge in the installation, commissioning, and operation of the equipment;

- Are familiar with the working field where it is being installed;

- Are able to safely perform operations in accordance with accepted safety engineering steps;

- Are authorized to energize and de-energize equipment, and to isolate, ground, and label it;

- Are trained in the maintenance and use of safety apparatus in accordance with safety engineering regulations;

- Have been trained in first aid if any emergency situations happen.

## **Warning Indications**

The following indicators and standard definitions are used:

**DANGER!** means that death, severe personal injury and considerable equipment damage will occur if safety precautions are disregarded.

WARNING! means that death, severe personal and considerable equipment damage could occur if safety precautions are disregarded.

A CAUTION! means that light personal injury or equipment damage may occur if safety precautions are disregarded.

NOTICE! is particularly applies to damage to device and to resulting damage of the protected equipment.

#### DANGER!

NEVER allow the current transformer (CT) secondary circuit connected to this equipment to be opened while the primary system is live. Opening the CT circuit will produce a dangerously high voltage.

#### **WARNING!**

**ONLY** qualified personnel should work on or in the vicinity of this device. This personnel MUST be familiar with all safety regulations and service procedures described in this manual. During operating of electrical device, certain part of the device is under high voltage. Severe personal injury and significant device damage could result from improper behavior.

#### **WARNING!**

Do **NOT** touch the exposed terminals of this device while the power supply is on. The generated high voltage causes death, injury, and device damage.

#### WARNING!

Thirty seconds is **NECESSARY** for discharging the voltage. Hazardous voltage can be present in the DC circuit just after switching off the DC power supply.

#### **CAUTION!**

#### Earthing

Securely earthed the earthing terminal of the device.

#### Operating environment

**ONLY** use the device within the range of ambient environment and in an environment free of abnormal vibration.

#### Ratings

Check the input ratings **BEFORE** applying AC voltage/current and power supply to the device.

#### Printed circuit board

Do **NOT** attach or remove printed circuit board if the device is powered on.

#### External circuit

Check the supply voltage used when connecting the device output contacts to external circuits, in order to prevent overheating.

#### Connection cable

Carefully handle connection cables without applying excessive force.

#### **NOTICE!**

The firmware may be upgraded to add new features or enhance/modify existing features, please **MAKE SURE** that the version of this manual is compatible with the product in your hand.

## Copyright © 2017 CYG SUNRI CO., LTD. All rights reserved.

This document contains confidential information of CYG SUNRI CO., LTD. Any improper use of the document or information contained herein in any way (including, but not limited to, total or partial disclosure, reproduction, or dissemination) by organizations or persons is prohibited. CYG SUNRI CO., LTD. reserve all rights to this document and to the information contained herein.

CYG SUNRI CO., LTD. has made every effort to ensure that this document is accurate. CYG SUNRI CO., LTD. disclaims liability for any inaccuracies or omissions that may have occurred. If nevertheless any incorrect, misleading, or incomplete information are found, comments and suggestions for correction or improvement are greatly appreciated. CYG SUNRI CO., LTD. reserves the rights to upgrade

PRS-753 iii

the products and to make improvements to the documents without notice.

The users are responsible for understanding the information and should not rely on this information as absolute. If the users do act upon the suggestions contained in this document, the users should be responsible for themself and their actions.

CYG SUNRI CO., LTD.

Tel: +86-400-678-8099

Headquarters: No.13, Keji North 1st Road, North Area of Hi-tech

Industral Park, Nanshan District, Shenzhen, China

Website: http://www.sznari.com

P/N: ZL\_PRS-753\_X\_Instruction Manual\_EN\_Overseas General\_X

Version: 2.06

#### **Documentation Outline**

The manual provides a functional and technical description of this relay and a comprehensive set of instructions for the relay's use and application.

All contents provided by this manual are summarized as below:

## 1 Briefly Introduction

Briefly introduce the application scope, the selectable functions and product features about this equipment.

#### 2 Technical Specifications

Introduce the technical specifications about this relay, including electrical specifications, mechanical specifications, ambient temperature and humidity range, communication interface parameters, type tests, setting ranges and accuracy limits etc.

#### **3 Protection Functions**

Provide a comprehensive and detailed protection function description of all protection modules.

#### **4 Supervision Functions**

Introduce the automatic self-supervision function of this equipment.

#### 5 Monitoring & Control

Introduce the measurement, controlling, signaling, recording and other functions of this relay.

#### 6 Hardware

Introduce the main module functions of this relay and describe the definition of all terminals of each module.

#### 7 Human Machine Interface

Include all the menus of device.

#### **8 Configuration Function**

Introduce the configurable function (such as protection function configuration, LED configuration, binary input configuration and binary output configuration, analog quantities channels etc.) of this relay.

#### 9 Communication Protocol

Introduce the communication interfaces and protocol that this relay contains. IEC60970-5-103 and IEC61850 protocols are introduced in details.

## 10 Commissioning

Introduce how to commission this relay, check the calibration and test all the function of this relay.

#### 11 Installation

Recommend on unpacking, handling, inspection and storage of this relay. A guide to the mechanical installation and electrical wiring of this relay is also provided, including earthing recommendations. Some typical wiring connection is demonstrated in this manual as well.

#### 12 Maintenance

A general maintenance steps for this device is outlined.

## 14 Connection Diagrams

List the connection diagram examples including all types of modules.

## 15 Manual Version History

List the instruction manual versions and their corresponding modification history records.

# **Table of contents**

| Preface                                    | i  |

|--------------------------------------------|----|

| User's Guideline                           | i  |

| Personnel Security                         | i  |

| Warning Indications                        | ii |

| Documentation Outline                      | iv |

| Table of contents                          | 1  |

| 1 Briefly Introduction                     | 14 |

| 1.1 Application Scope                      | 14 |

| 1.2 Product Function                       | 14 |

| 1.3 Product Features                       | 15 |

| 2 Technical Specifications                 | 17 |

| 2.1 Electrical Specifications              | 17 |

| 2.1.1 Current Transformer Ratings          | 17 |

| 2.1.2 Voltage Transformer Ratings          | 17 |

| 2.1.3 Auxiliary Power Supply               | 17 |

| 2.1.4 Binary Input                         | 18 |

| 2.1.5 Binary Output                        | 18 |

| 2.2 Mechanical Specifications              | 18 |

| 2.3 Ambient Temperature and Humidity Range | 19 |

| 2.4 Communication Interfaces               | 19 |

| 2.4.1 Ethernet Port                        | 19 |

| 2.4.2 Serial Port                          | 20 |

| 2.4.3 Time Synchronization                 | 20 |

| 2.4.4 Ethernet Port for Debugging          | 20 |

| 2.5 Type Tests                             | 20 |

| 2.5.1 Environmental Tests                  | 20 |

| 2.5.2 Mechanical Tests                     | 21 |

| 2.5.3 Electrical Tests                                     | 21 |

|------------------------------------------------------------|----|

| 2.5.4 Electromagnetic Compatibility                        | 22 |

| 2.6 Terminals                                              | 23 |

| 2.7 Measurement Range and Accuracy                         | 23 |

| 2.8 Protective Functions                                   | 23 |

| 2.8.1 Fault Detector                                       | 23 |

| 2.8.2 Line Differential Protection                         | 23 |

| 2.8.3 Distance Protection                                  | 24 |

| 2.8.4 Three Phase Directional Overcurrent Protection       | 24 |

| 2.8.5 Directional Earth Fault Protection                   | 24 |

| 2.8.6 Directional Negative-sequence Overcurrent Protection | 24 |

| 2.8.7 Breaker Failure Protection                           | 24 |

| 2.8.8 Thermal Overload Protection                          | 25 |

| 2.8.9 Stub Differential Protection                         | 25 |

| 2.8.10 Pole Discordance Protection                         | 25 |

| 2.8.11 Reverse Power Protection                            | 25 |

| 2.8.12 Broken Conductor Protection                         | 25 |

| 2.8.13 Three Phase Overvoltage Protection                  | 25 |

| 2.8.14 Residual Overvoltage Protection                     | 25 |

| 2.8.15 Three Phase Undervoltage Protection                 | 26 |

| 2.8.16 Overfrequency Protection                            | 26 |

| 2.8.17 Underfrequency Protection                           | 26 |

| 2.8.18 Auto-reclosing                                      | 26 |

| 2.8.19 Transient Overreach                                 | 26 |

| 2.8.20 Fault Locator                                       | 26 |

| 3 Protection Functions                                     | 27 |

| 3.1 Overview                                               | 27 |

| 3.2 System Parameters                                      | 29 |

| 3.2.1 Overview                                             | 29 |

| 3.2.2 Settings                                             | 29 |

| 3.3 Line Parameters                                       | 30 |

|-----------------------------------------------------------|----|

| 3.3.1 Overview                                            | 30 |

| 3.3.2 Settings                                            | 30 |

| 3.4 Fault Detector FD                                     | 30 |

| 3.4.1 Overview                                            | 30 |

| 3.4.2 Protection Principle                                | 31 |

| 3.4.3 Logic                                               | 34 |

| 3.4.4 Settings                                            | 35 |

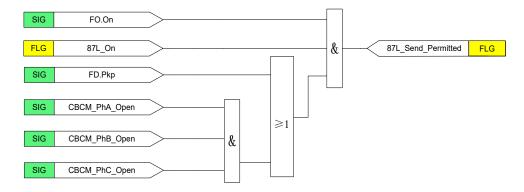

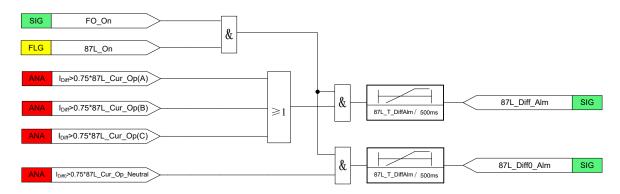

| 3.5 Line Differential Protection 87L                      | 35 |

| 3.5.1 Overview                                            | 35 |

| 3.5.2 Protection Principle                                | 37 |

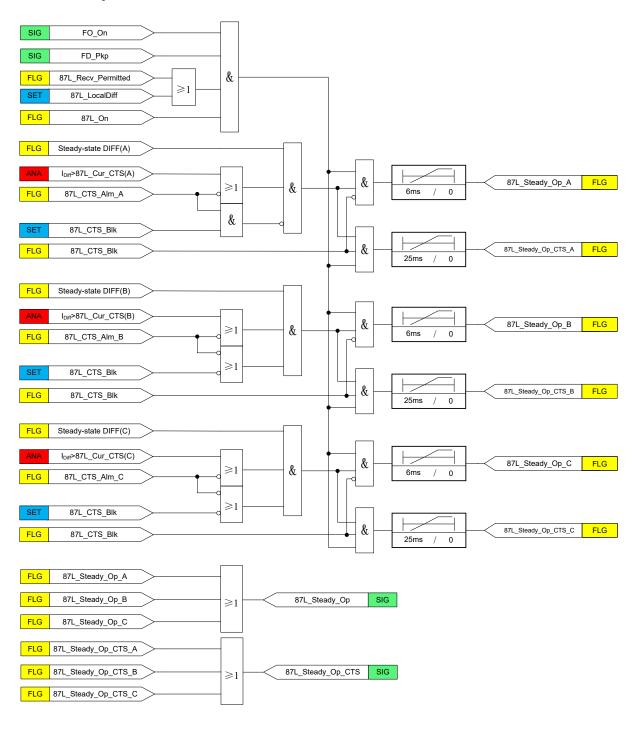

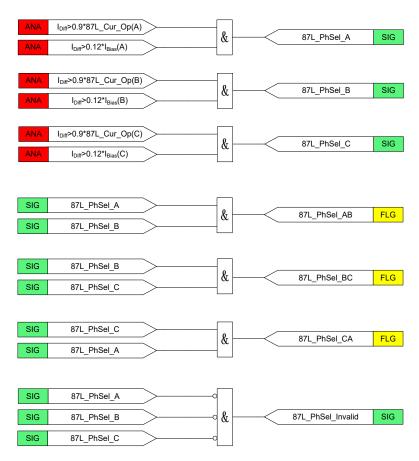

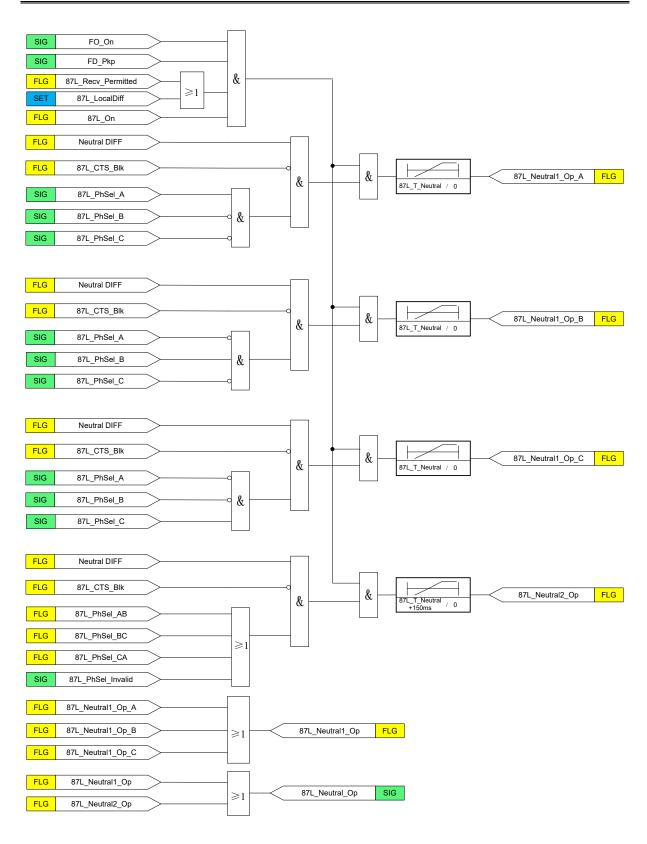

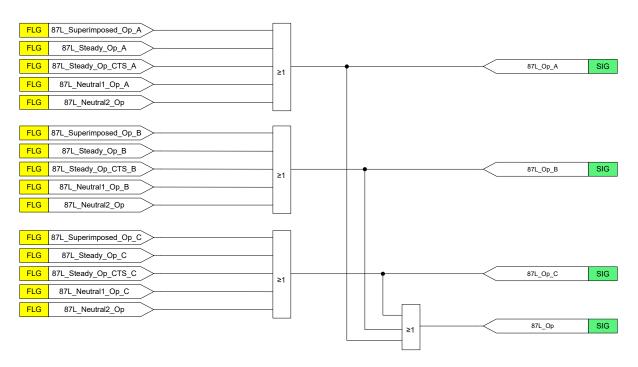

| 3.5.3 Logic                                               | 44 |

| 3.5.4 Settings                                            | 50 |

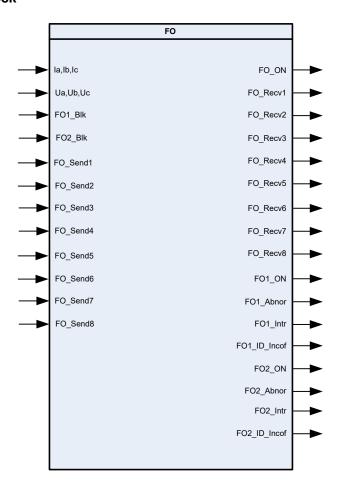

| 3.6 Optical Fiber Communication FO                        | 52 |

| 3.6.1 Overview                                            | 52 |

| 3.6.2 Protection Principle                                | 54 |

| 3.6.3 Logic                                               | 58 |

| 3.6.4 Settings                                            | 58 |

| 3.7 Distance Protection 21                                | 59 |

| 3.7.1 Overview                                            | 59 |

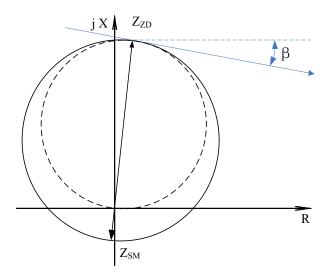

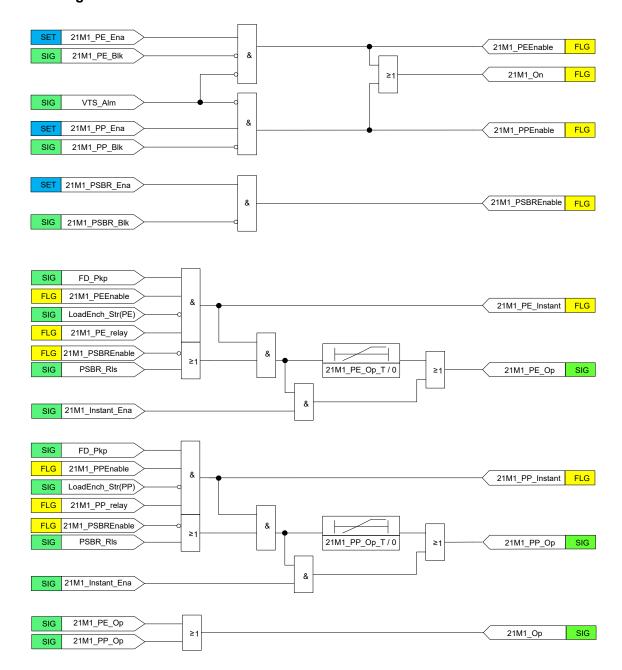

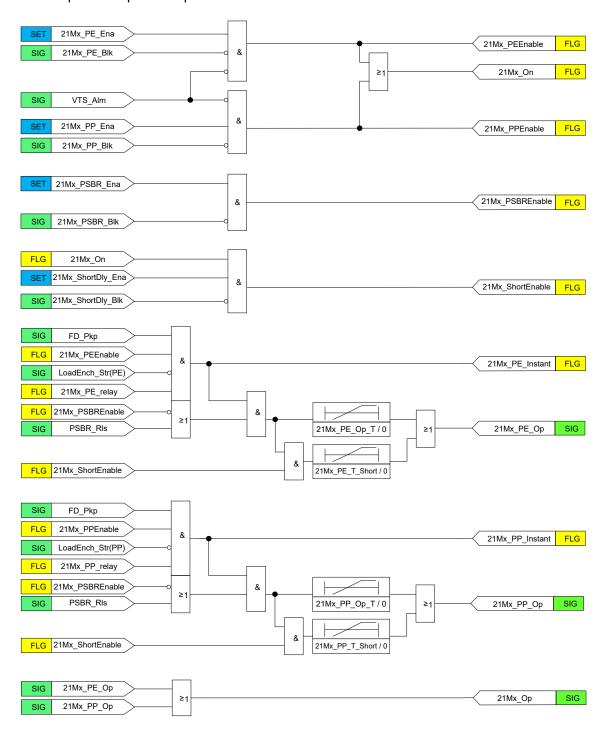

| 3.7.2 Mho Distance Protection 21M                         | 60 |

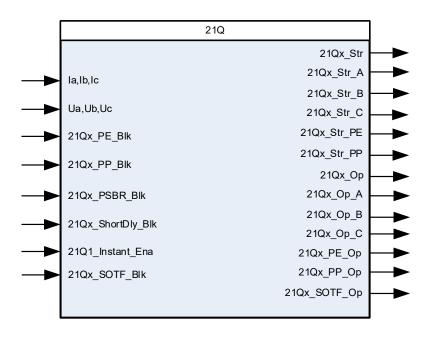

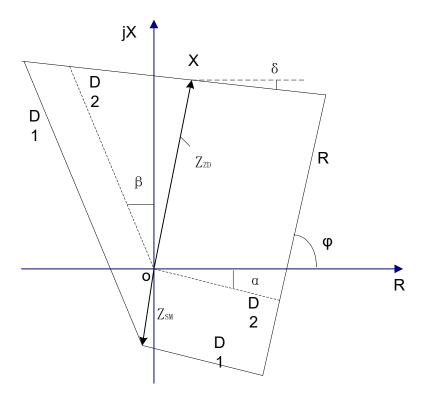

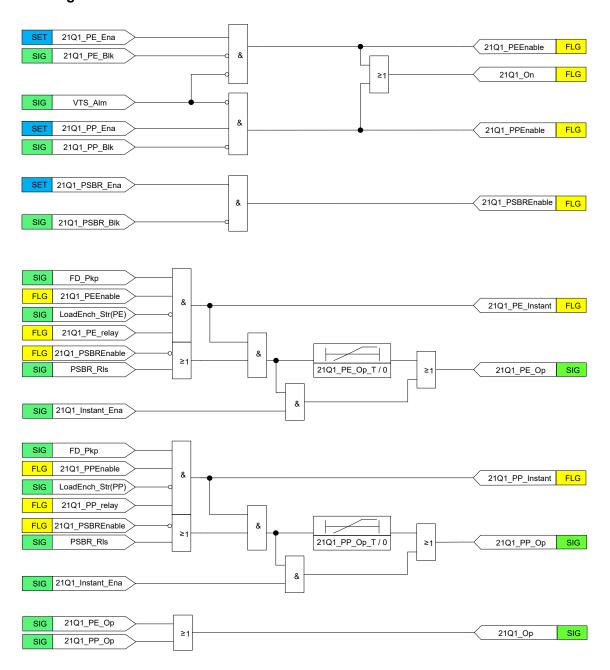

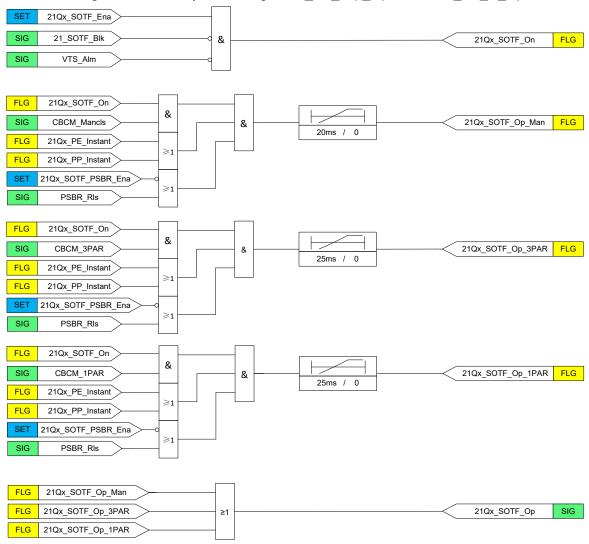

| 3.7.3 Quadrilateral Distance Protection 21Q               | 70 |

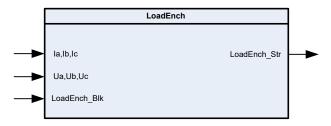

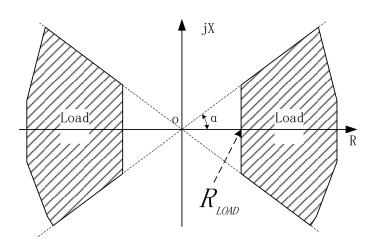

| 3.7.4 Load Encroachment LoadEnch                          | 79 |

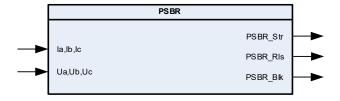

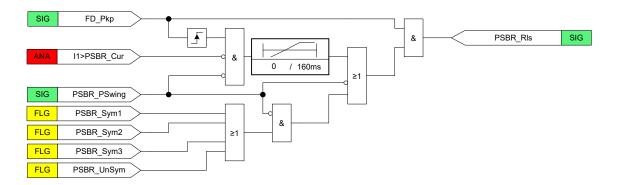

| 3.7.5 Power Swing Blocking Releasing PSBR                 | 81 |

| 3.8 Out-of-Step Protection 780                            | 84 |

| 3.8.1 Overview                                            | 84 |

| 3.8.2 Protection Principle                                | 85 |

| 3.8.3 Logic                                               | 89 |

| 3.8.4 Settings                                            | 91 |

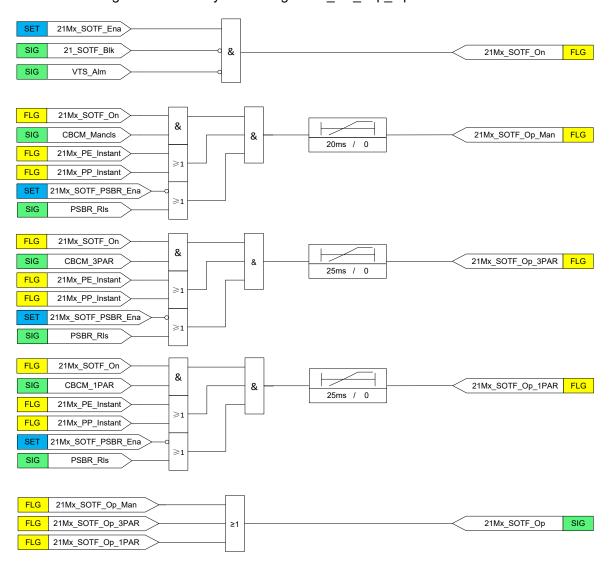

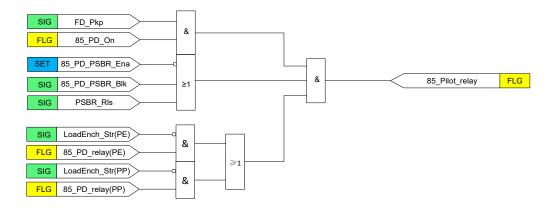

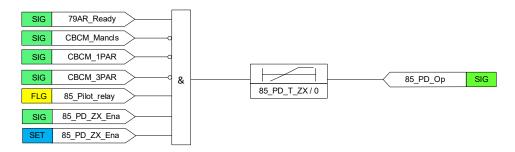

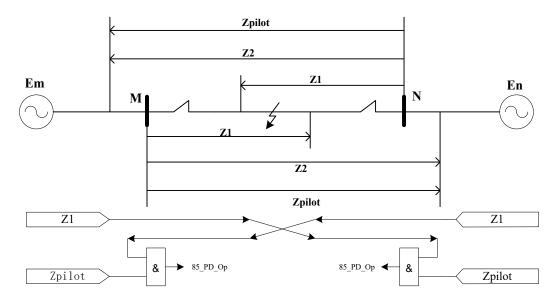

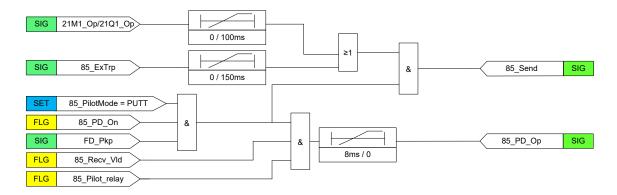

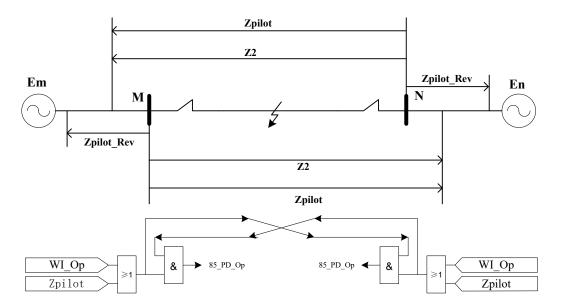

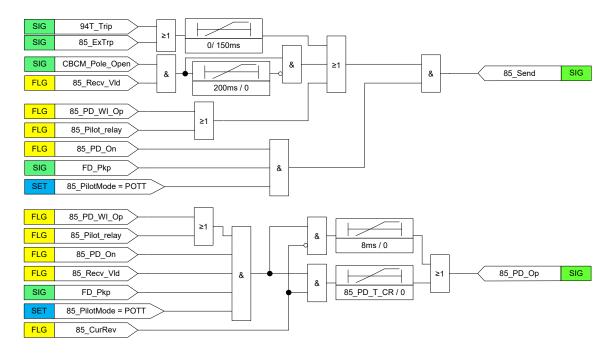

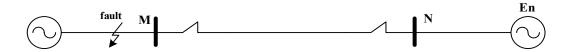

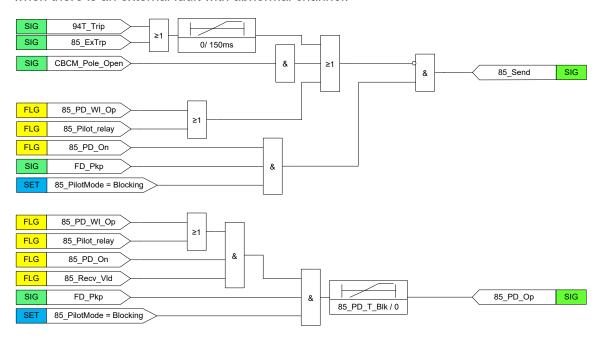

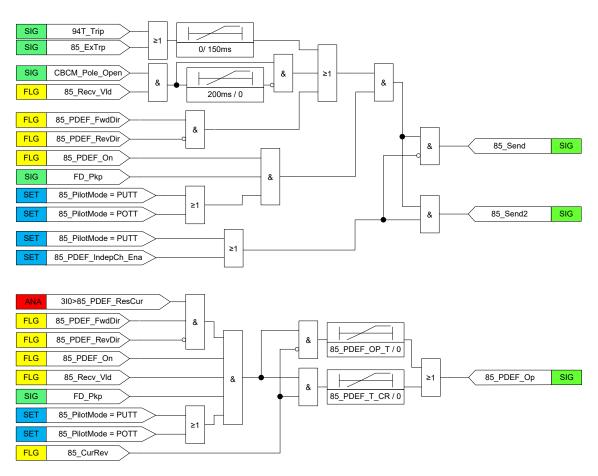

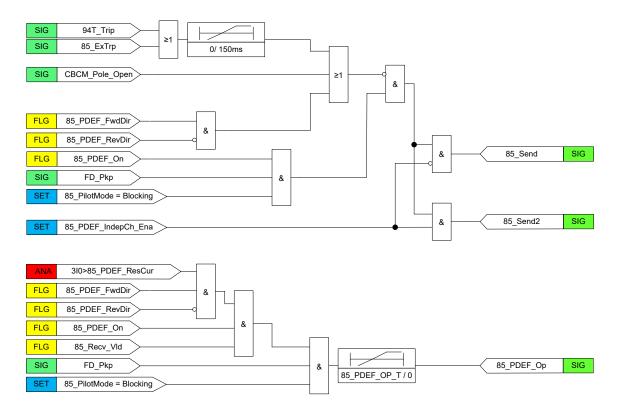

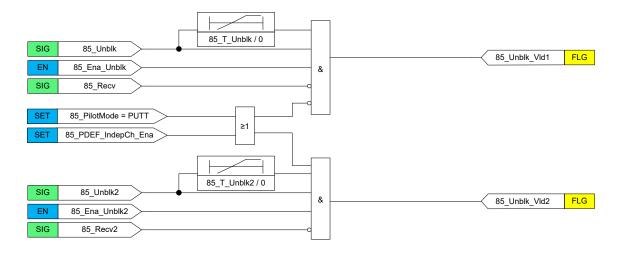

| 3.9 Scheme communication logic for distance protection 85 | 92 |

| 3.9.1 Overview                                                        | 92         |

|-----------------------------------------------------------------------|------------|

| 3.9.2 Protection Principle                                            | 94         |

| 3.9.3 Settings                                                        | 103        |

| 3.10 Scheme communication logic for directional earth fault protectio | n 85N .106 |

| 3.10.1 Overview                                                       | 106        |

| 3.10.2 Protection Principle                                           | 108        |

| 3.10.3 Settings                                                       | 112        |

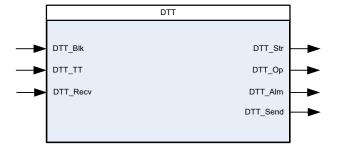

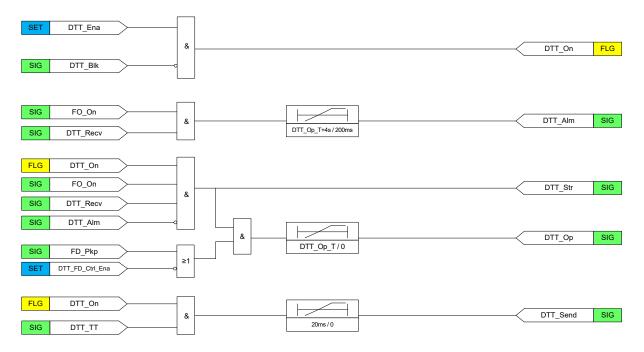

| 3.11 Direct Transfer Trip Logic DTT                                   | 113        |

| 3.11.1 Overview                                                       | 113        |

| 3.11.2 Protection Principle                                           | 114        |

| 3.11.3 Logic                                                          | 114        |

| 3.11.4 Settings                                                       | 114        |

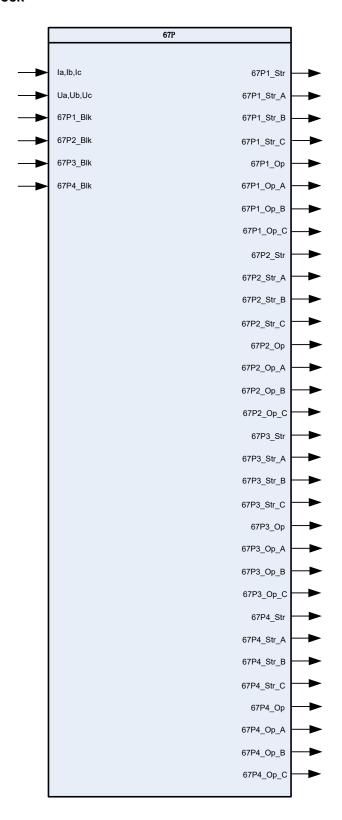

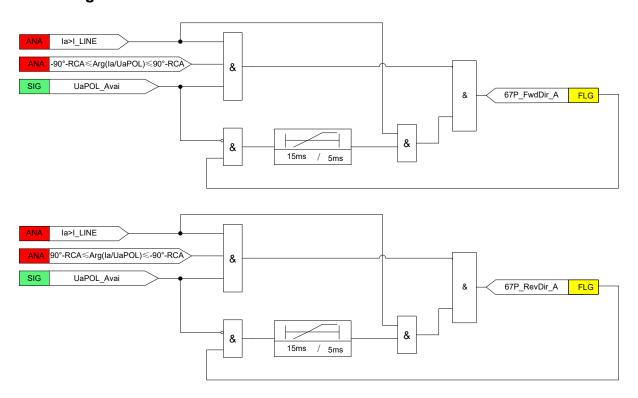

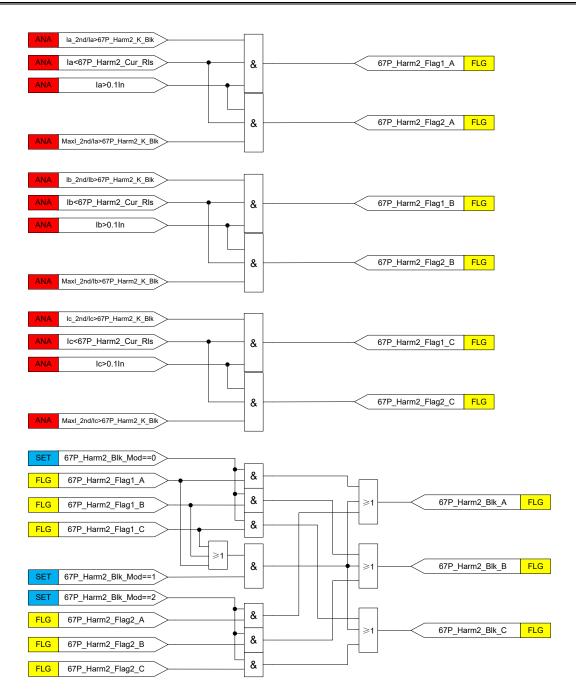

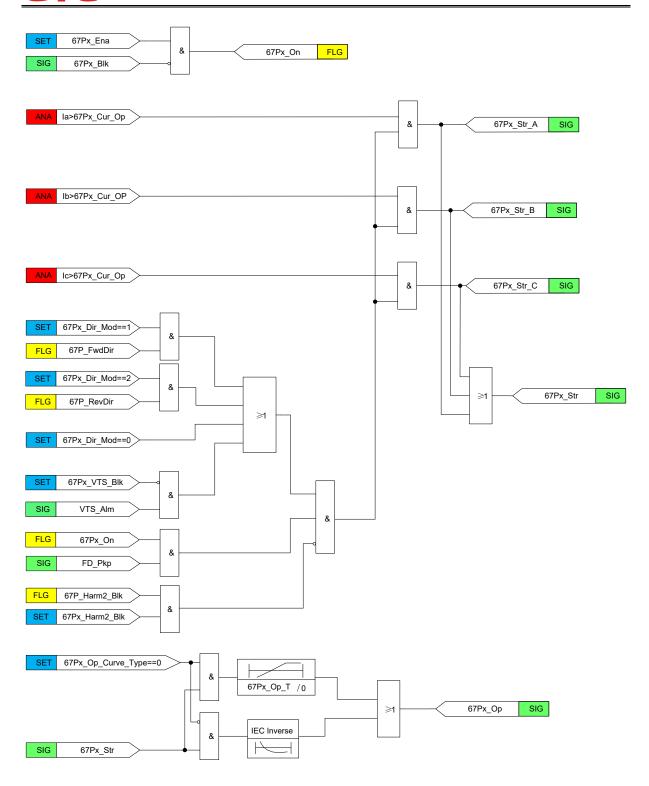

| 3.12 Three Phase Directional Overcurrent Protection 67P               | 115        |

| 3.12.1 Overview                                                       | 115        |

| 3.12.2 Protection Principle                                           | 118        |

| 3.12.3 Logic                                                          | 121        |

| 3.12.4 Settings                                                       | 124        |

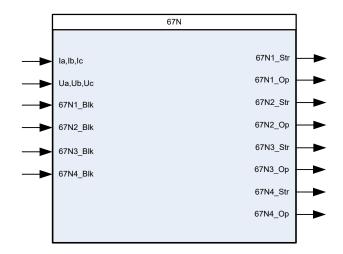

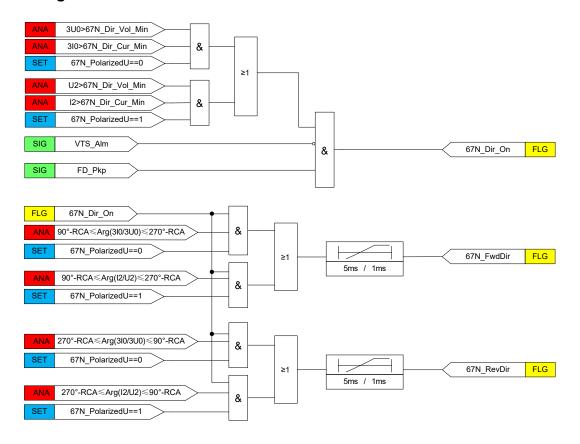

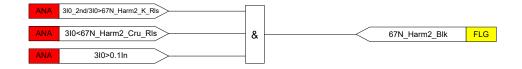

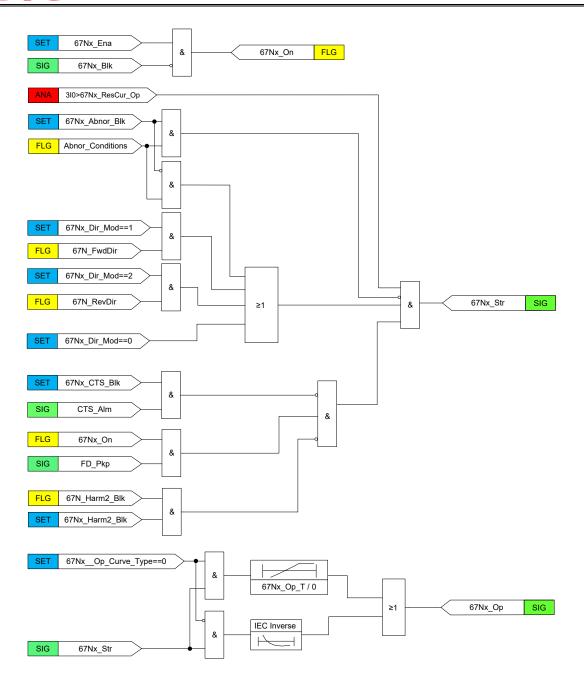

| 3.13 Directional Earth Fault Overcurrent Protection 67N               | 126        |

| 3.13.1 Overview                                                       | 126        |

| 3.13.2 Protection Principle                                           | 127        |

| 3.13.3 Logic                                                          | 130        |

| 3.13.4 Settings                                                       | 132        |

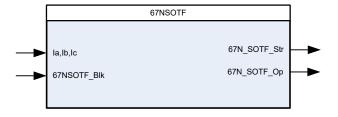

| 3.14 Residual Current SOTF Protection 67NSOTF                         | 134        |

| 3.14.1 Overview                                                       | 134        |

| 3.14.2 Protection Principle                                           | 135        |

| 3.14.3 Logic                                                          | 136        |

| 3.14.4 Settings                                                       | 136        |

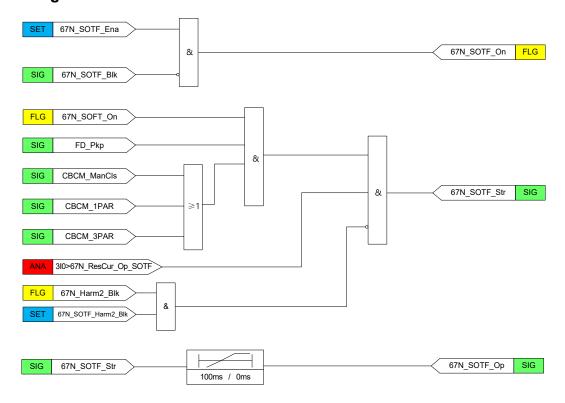

| 3.15 Directional Negative-sequence Overcurrent Protection 67I2        | 136        |

| 3.15.1 Overview                                                       | 136        |

| 3.15.2 Protection Principle                                           | 138        |

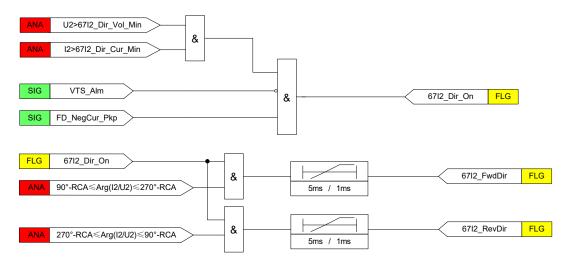

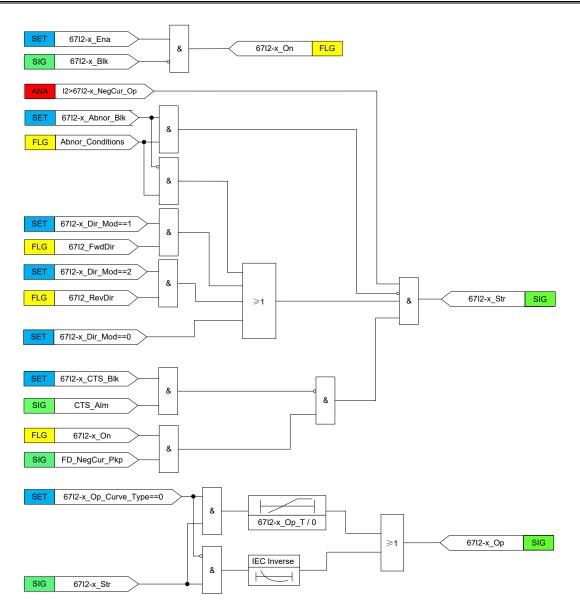

| 3.15.3 Logic                                                         | 140 |

|----------------------------------------------------------------------|-----|

| 3.15.4 Settings                                                      | 141 |

| 3.16 Phase Overcurrent Protection for VT Circuit Failure 51PVT       | 143 |

| 3.16.1 Overview                                                      | 143 |

| 3.16.2 Protection Principle                                          | 144 |

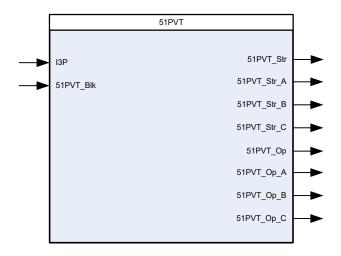

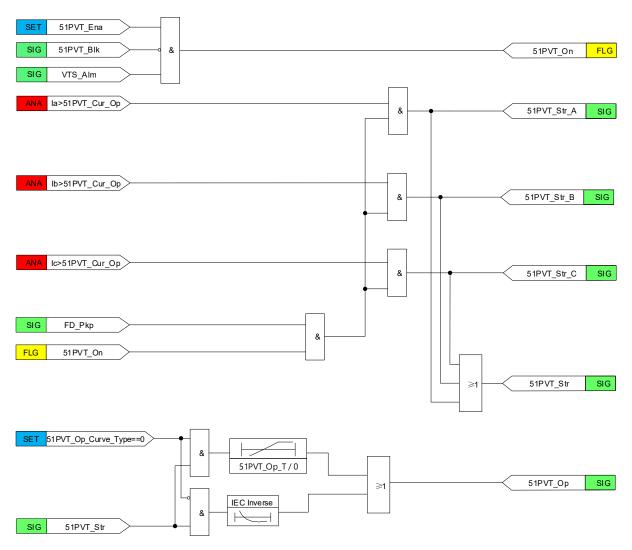

| 3.16.3 Logic                                                         | 146 |

| 3.16.4 Settings                                                      | 146 |

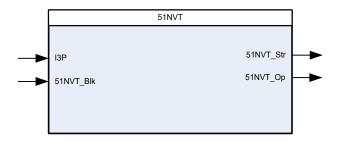

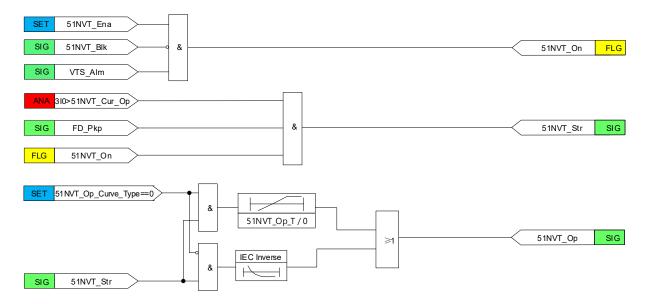

| 3.17 Earth Fault Overcurrent Protection for VT Circuit Failure 51NVT | 147 |

| 3.17.1 Overview                                                      | 147 |

| 3.17.2 Protection Principle                                          | 148 |

| 3.17.3 Logic                                                         | 149 |

| 3.17.4 Settings                                                      | 150 |

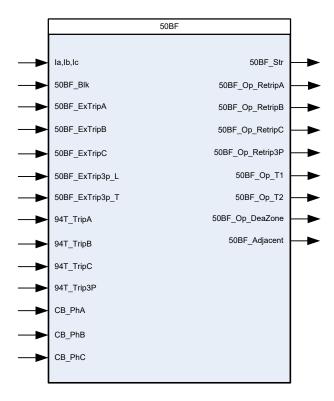

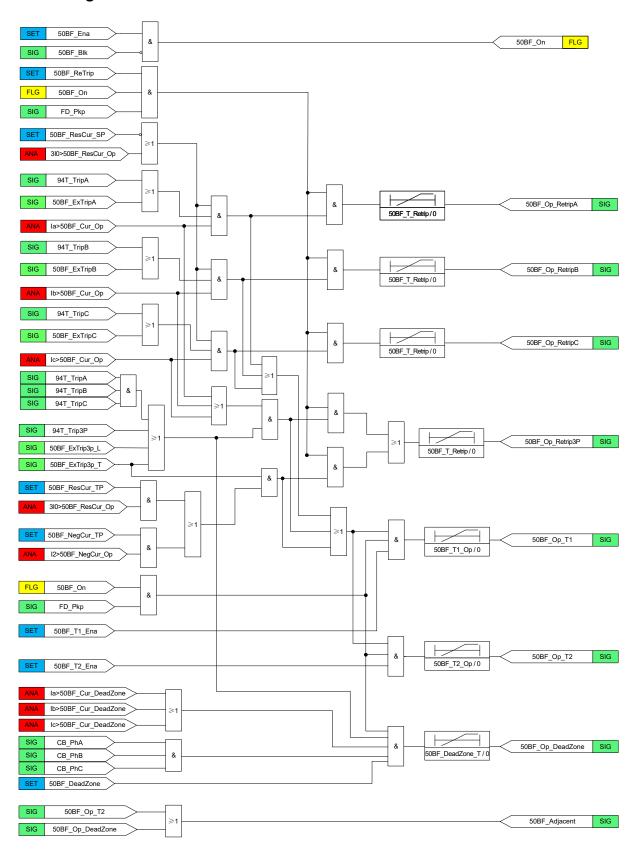

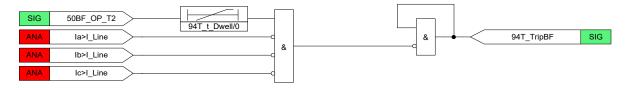

| 3.18 Breaker Failure Protection 50BF                                 | 151 |

| 3.18.1 Overview                                                      | 151 |

| 3.18.2 Protection Principle                                          | 152 |

| 3.18.3 Logic                                                         | 155 |

| 3.18.4 Settings                                                      | 156 |

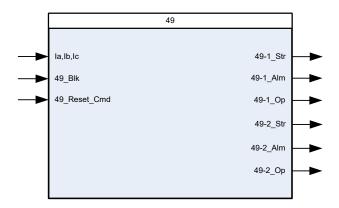

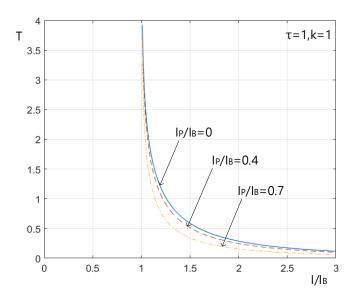

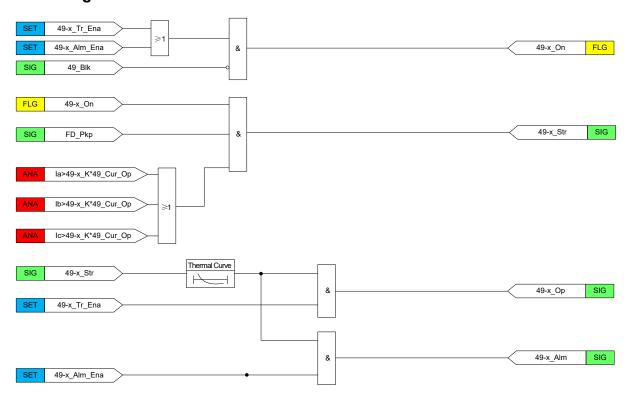

| 3.19 Thermal Overload Protection 49                                  | 157 |

| 3.19.1 Overview                                                      | 157 |

| 3.19.2 Operation Principle                                           | 158 |

| 3.19.3 Logic                                                         | 160 |

| 3.19.4 Settings                                                      | 160 |

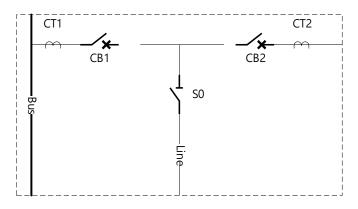

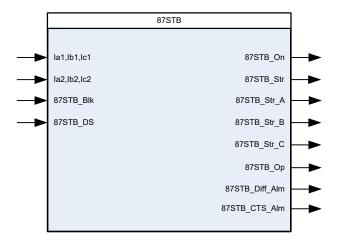

| 3.20 Stub Differential Protection 87STB                              | 161 |

| 3.20.1 Overview                                                      | 161 |

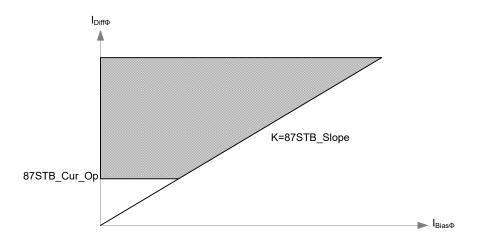

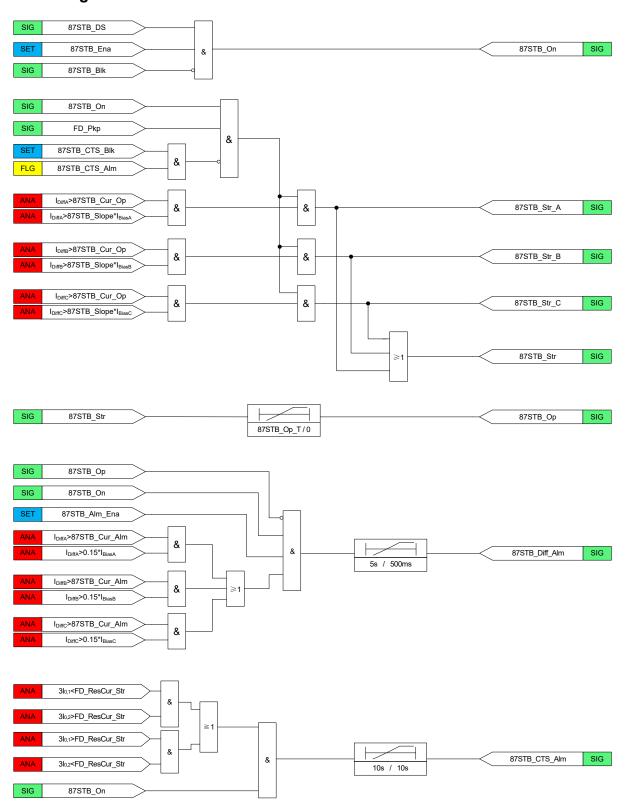

| 3.20.2 Operation Principle                                           | 162 |

| 3.20.3 Logic                                                         | 165 |

| 3.20.4 Settings                                                      | 166 |

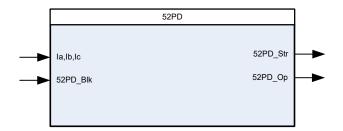

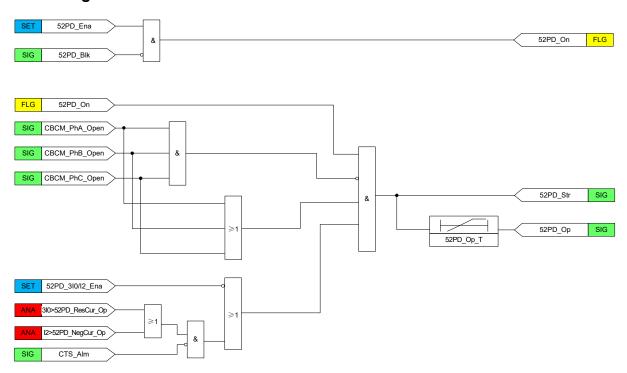

| 3.21 Pole Discordance Protection 52PD                                | 166 |

| 3.21.1 Overview                                                      | 166 |

| 3.21.2 Operation Principle                                           | 167 |

| 3.21.3 Logic                                 | 168 |

|----------------------------------------------|-----|

| 3.21.4 Settings                              | 168 |

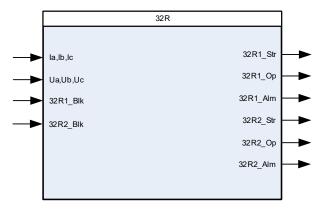

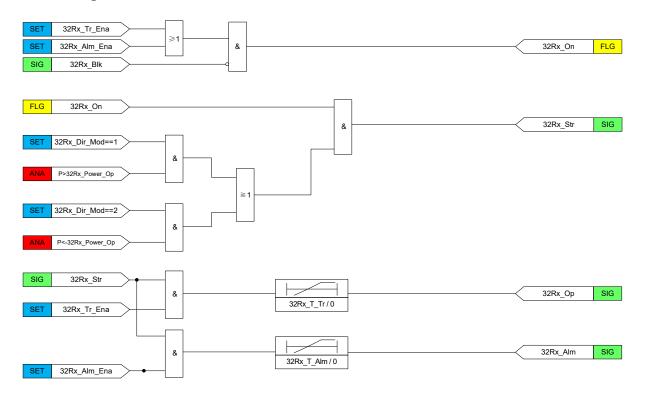

| 3.22 Reverse Power Protection 32R            | 169 |

| 3.22.1 Overview                              | 169 |

| 3.22.2 Operation Principle                   | 170 |

| 3.22.3 Logic                                 | 171 |

| 3.22.4 Settings                              | 171 |

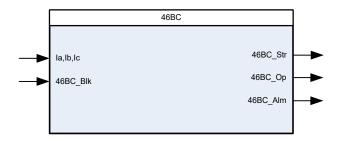

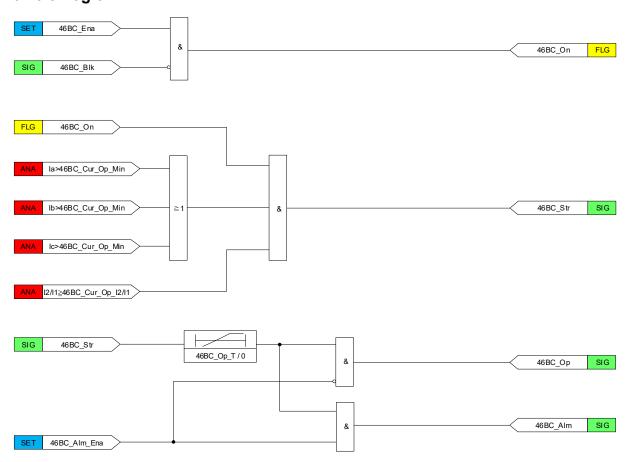

| 3.23 Broken Conductor Protection 46BC        | 172 |

| 3.23.1 Overview                              | 172 |

| 3.23.2 Protection Principle                  | 173 |

| 3.23.3 Logic                                 | 175 |

| 3.23.4 Settings                              | 175 |

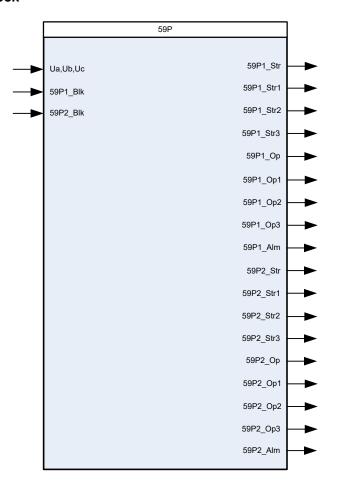

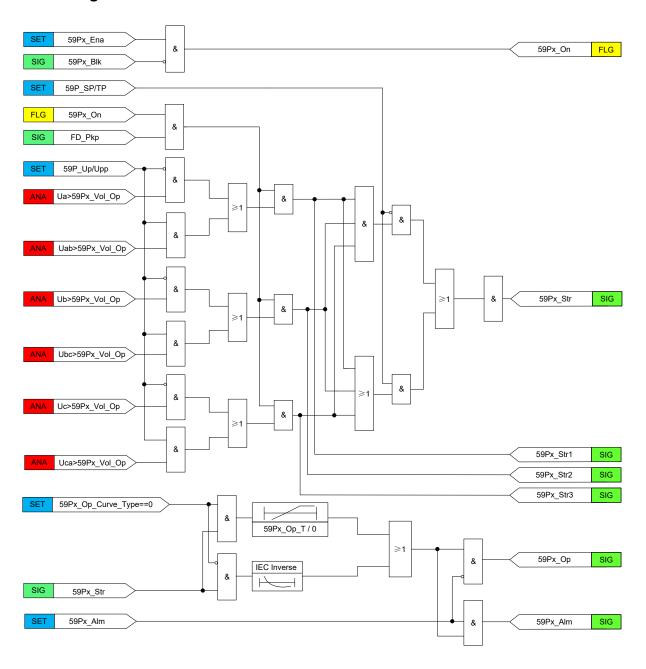

| 3.24 Three Phase Overvoltage Protection 59P  | 176 |

| 3.24.1 Overview                              | 176 |

| 3.24.2 Protection Principle                  | 178 |

| 3.24.3 Logic                                 | 180 |

| 3.24.4 Settings                              | 180 |

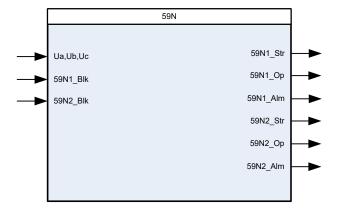

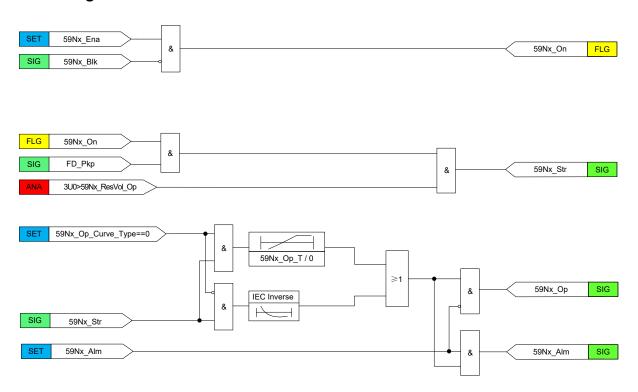

| 3.25 Residual Overvoltage Protection 59N     | 182 |

| 3.25.1 Overview                              | 182 |

| 3.25.2 Protection Principle                  | 183 |

| 3.25.3 Logic                                 | 184 |

| 3.25.4 Settings                              | 184 |

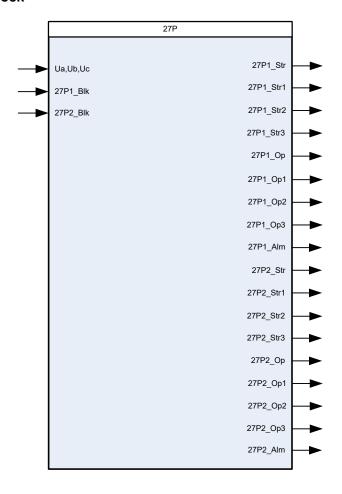

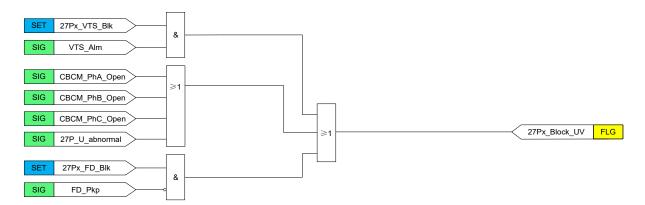

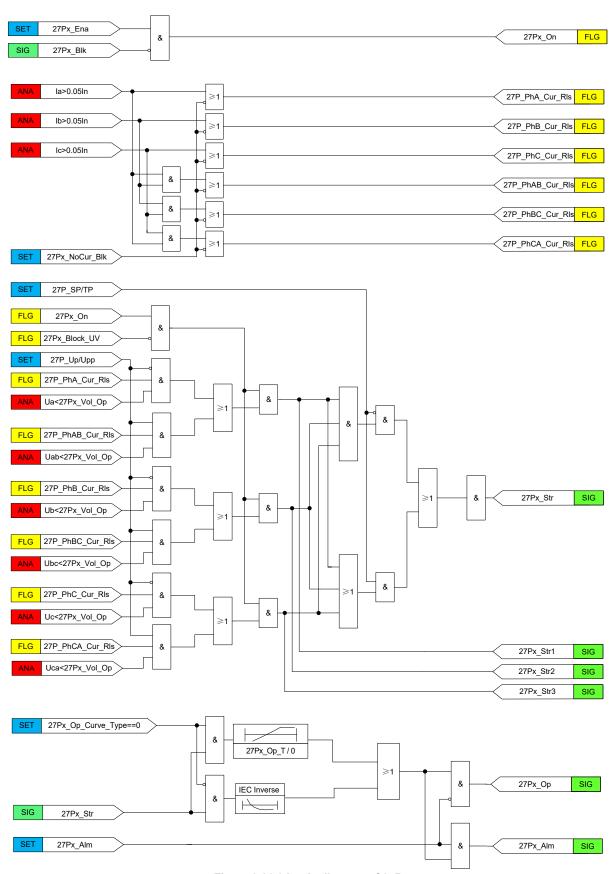

| 3.26 Three Phase Undervoltage Protection 27P | 185 |

| 3.26.1 Overview                              | 185 |

| 3.26.2 Protection Principle                  | 187 |

| 3.26.3 Logic                                 | 189 |

| 3.26.4 Settings                              | 191 |

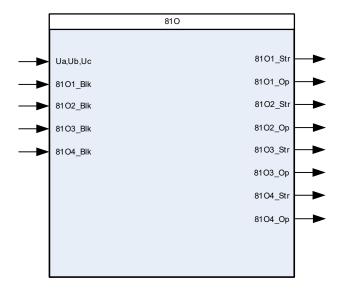

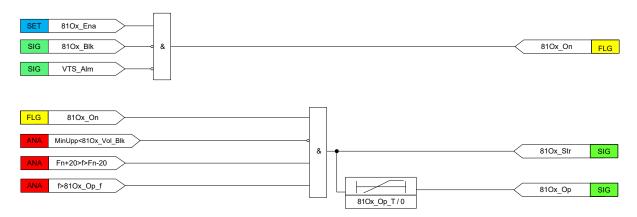

| 3.27 Overfrequency Protection 810            | 192 |

| 3.27.1 Overview                              | 192 |

| 3.27.2 Protection Principle                  | 194 |

| 3.27.3 Logic                           | 194 |

|----------------------------------------|-----|

| 3.27.4 Settings                        | 195 |

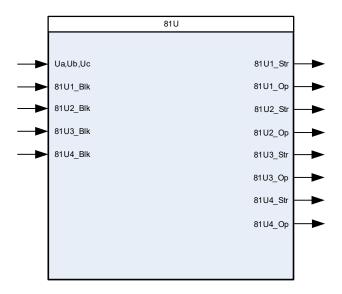

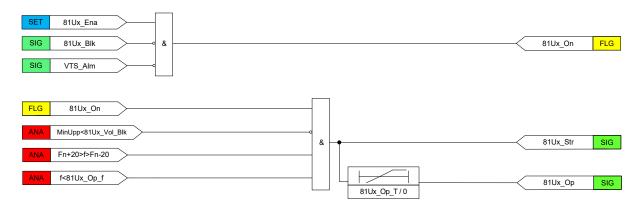

| 3.28 UnderFrequency Protection 81U     | 196 |

| 3.28.1 Overview                        | 196 |

| 3.28.2 Protection Principle            | 197 |

| 3.28.3 Logic                           | 198 |

| 3.28.4 Settings                        | 198 |

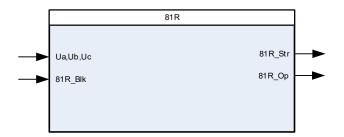

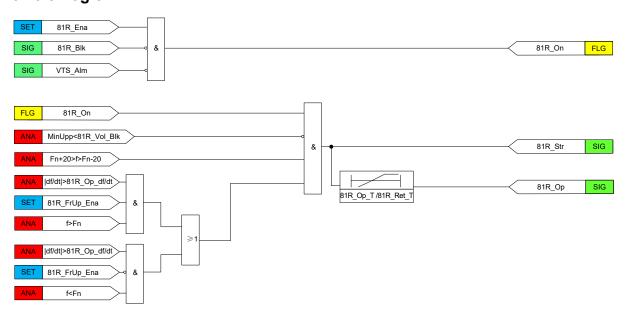

| 3.29 Frequency Gradient Protection 81R | 199 |

| 3.29.1 Overview                        | 199 |

| 3.29.2 Protection Principle            | 200 |

| 3.29.3 Logic                           | 201 |

| 3.29.4 Settings                        | 201 |

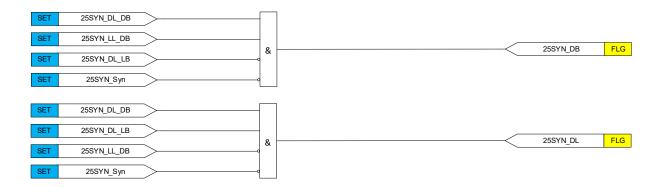

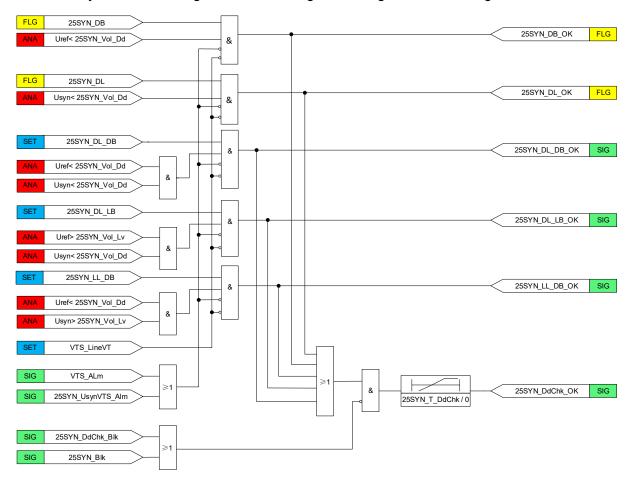

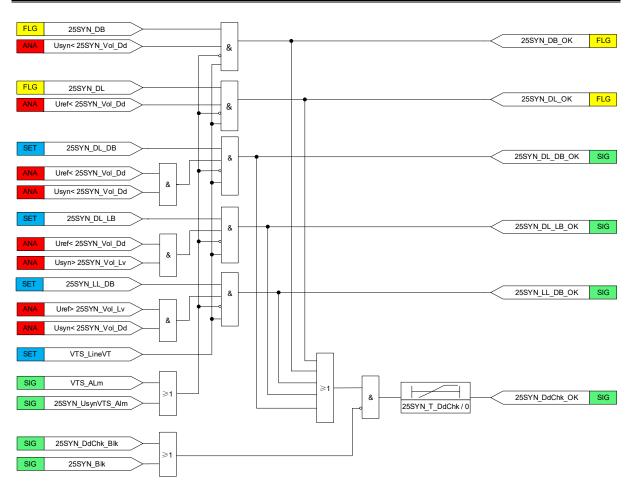

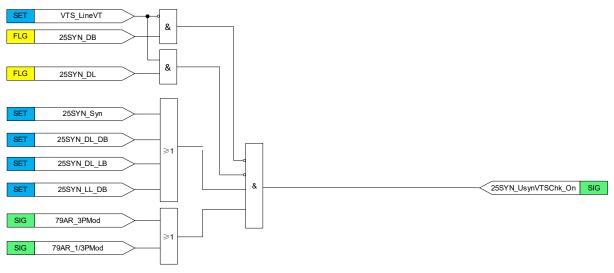

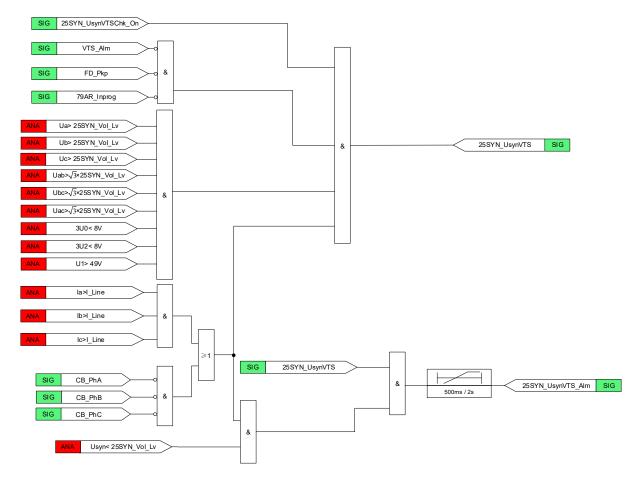

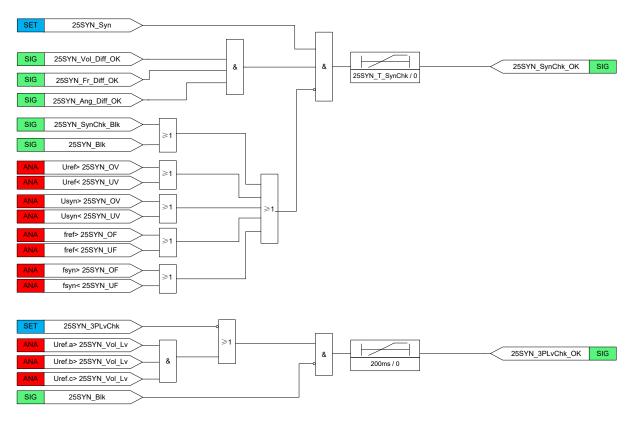

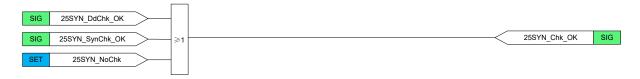

| 3.30 Synchrocheck 25SYN                | 202 |

| 3.30.1 Overview                        | 202 |

| 3.30.2 Operation Principle             | 203 |

| 3.30.3 Logic                           | 204 |

| 3.30.4 Settings                        | 208 |

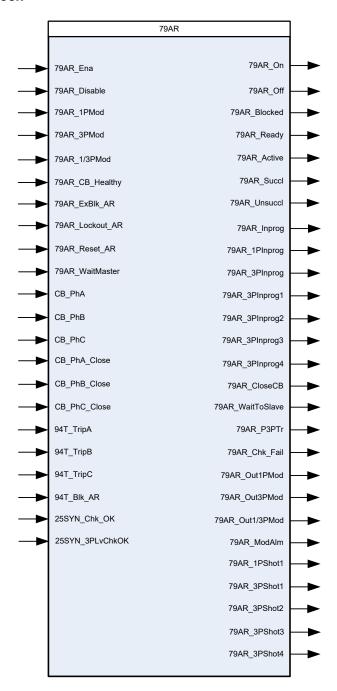

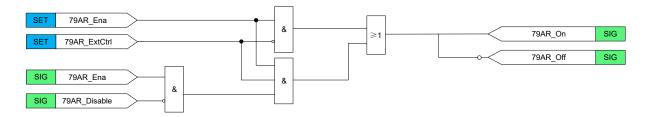

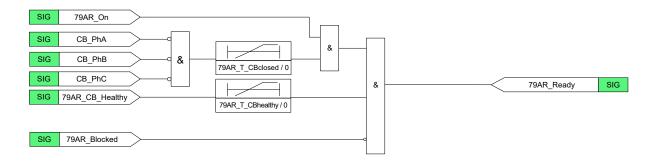

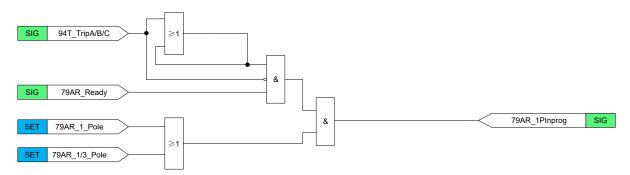

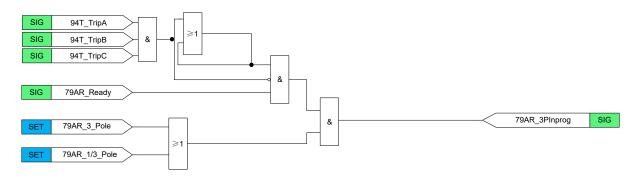

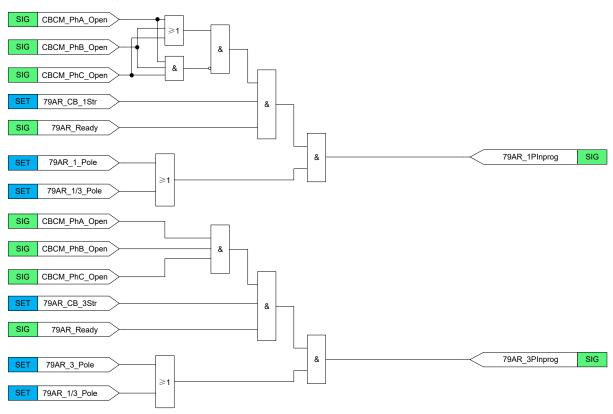

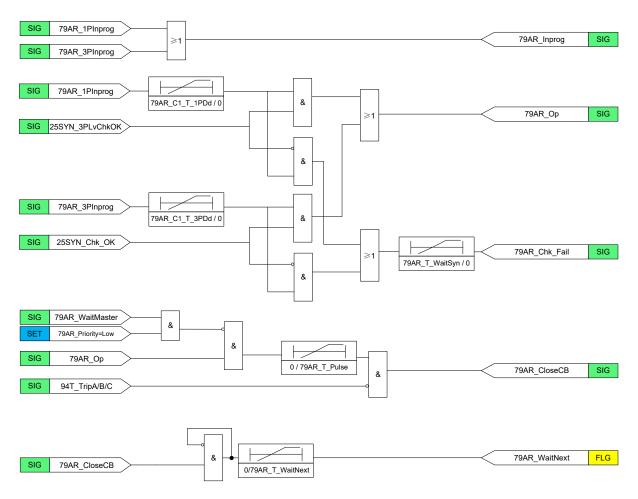

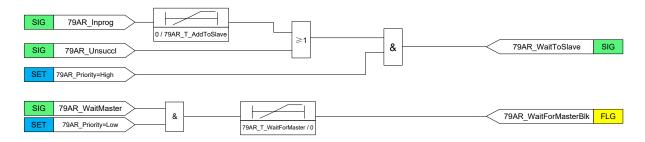

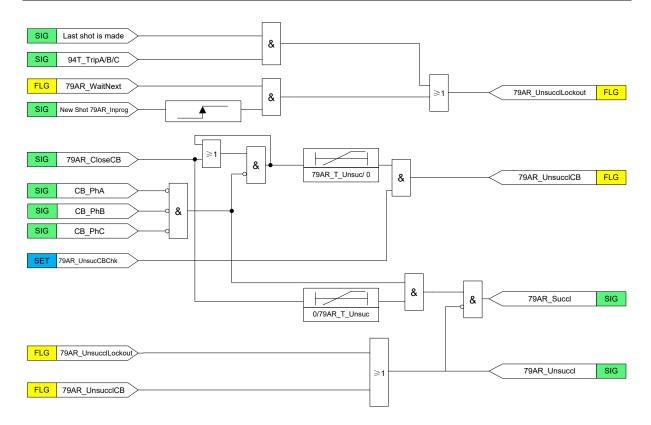

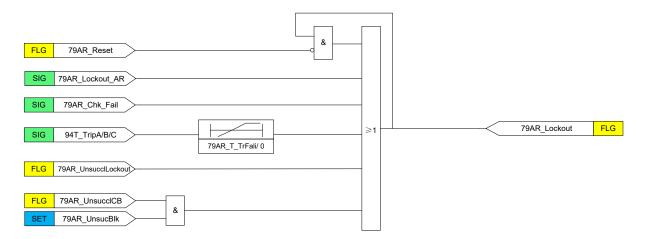

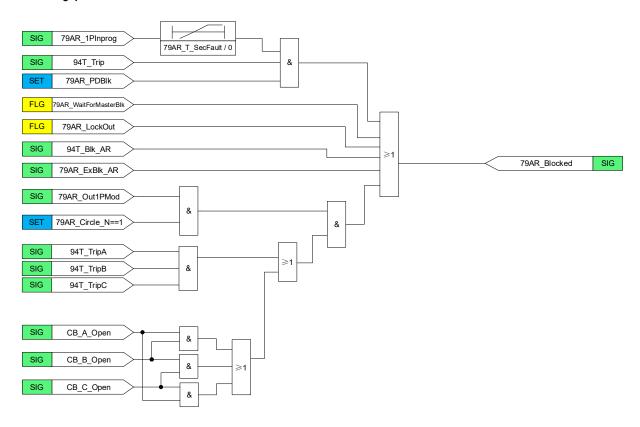

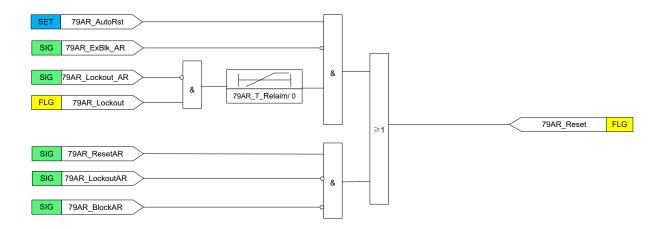

| 3.31 Automatic Reclosure 79AR          | 210 |

| 3.31.1 Overview                        | 210 |

| 3.31.2 Operation Principle             | 213 |

| 3.31.3 Settings                        | 221 |

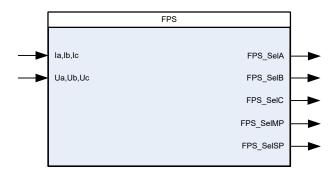

| 3.32 Faulty Phase Selection FPS        | 224 |

| 3.32.1 Overview                        | 224 |

| 3.32.2 Operation Principle             | 225 |

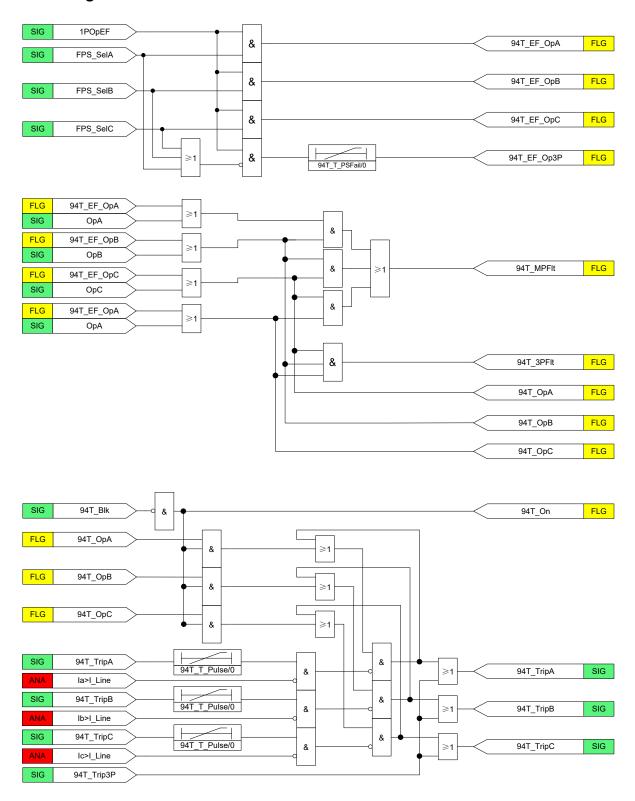

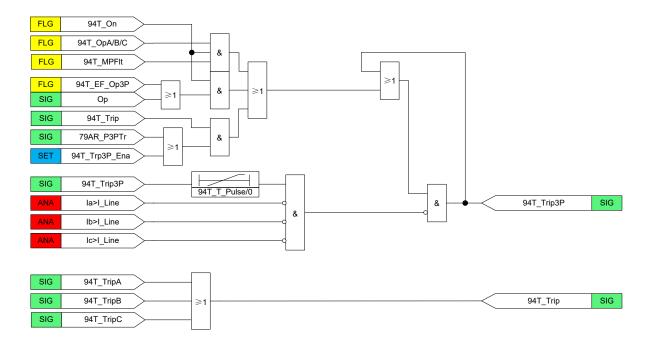

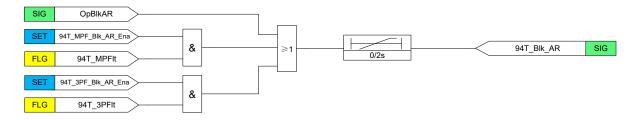

| 3.33 Trip Logic 94T                    | 226 |

| 3.33.1 Overview                        | 226 |

| 3.33.2 Operation Principle             | 228 |

| 3.33.3 Logic                           | 230 |

| 3.33.4 Settings                        | 231 |

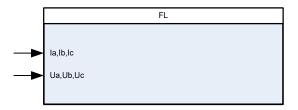

| 3.34 Fault Locator FL                  | 232 |

| 3.34.1 Overview                                                               | 232 |

|-------------------------------------------------------------------------------|-----|

| 3.34.2 Operation Principle                                                    | 233 |

| 3.35 General function block                                                   | 233 |

| 3.35.1 IDMT curves for over quantity protection and under quantity protection | 233 |

| 4 Supervision Functions                                                       | 235 |

| 4.1 Overview                                                                  | 235 |

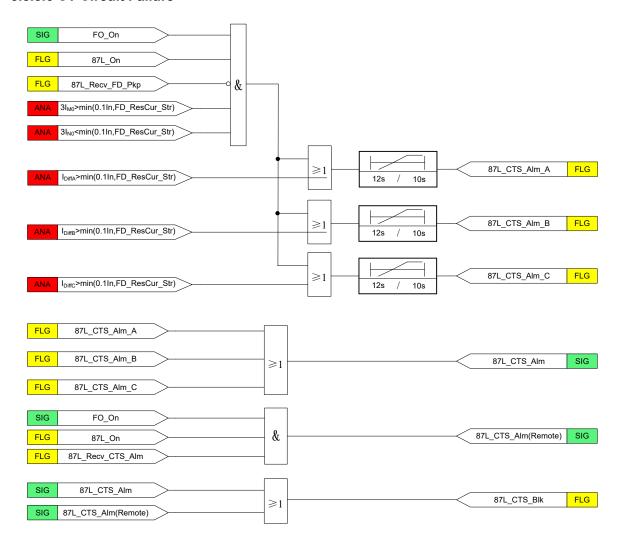

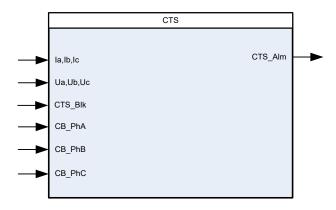

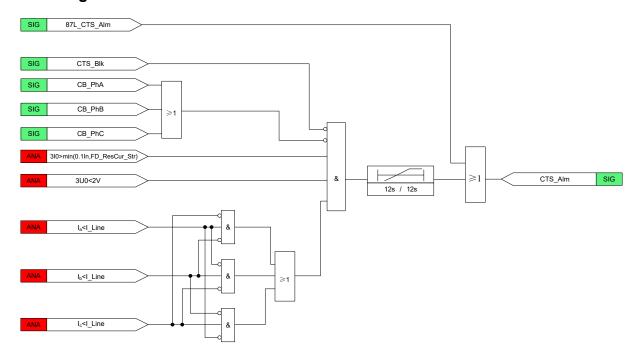

| 4.2 CT Circuit Supervision CTS                                                | 235 |

| 4.2.1 Overview                                                                | 235 |

| 4.2.2 Operation Principle                                                     | 236 |

| 4.2.3 Logic                                                                   | 236 |

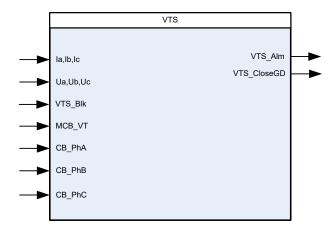

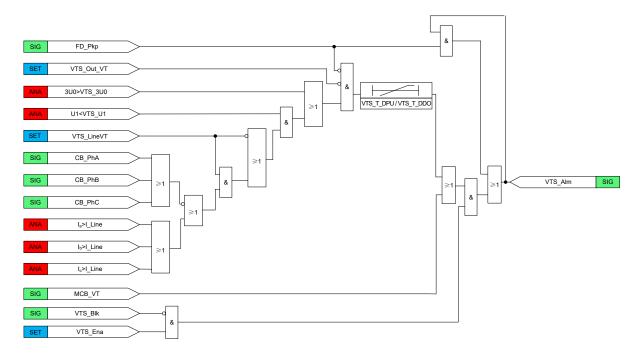

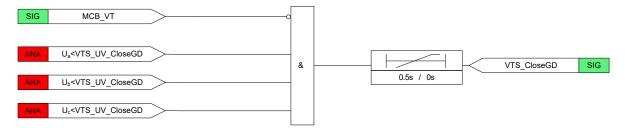

| 4.3 VT Circuit Supervision VTS                                                | 236 |

| 4.3.1 Overview                                                                | 236 |

| 4.3.2 Operation Principle                                                     | 237 |

| 4.3.3 Logic                                                                   | 239 |

| 4.3.4 Settings                                                                | 240 |

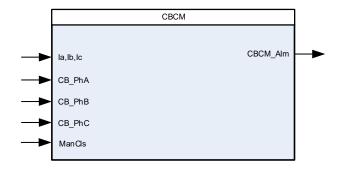

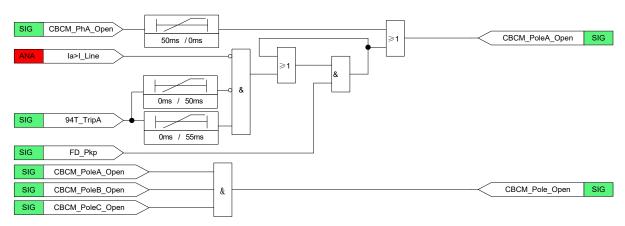

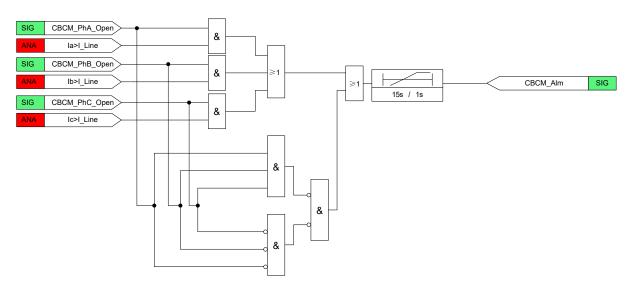

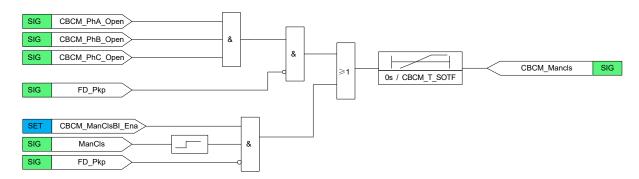

| 4.4 CB Position Supervision CBCM                                              | 240 |

| 4.4.1 Overview                                                                | 240 |

| 4.4.2 Operation Principle                                                     | 241 |

| 4.4.3 Logic                                                                   | 241 |

| 4.4.4 Settings                                                                | 243 |

| 4.5 Supervision Alarm and Block                                               | 243 |

| 5 Monitor & Control                                                           | 246 |

| 5.1 Overview                                                                  | 246 |

| 5.2 Measurement                                                               | 246 |

| 5.2.1 Protection Sampling                                                     | 246 |

| 5.2.2 Metering                                                                | 246 |

| 5.2.3 Settings                                                                | 246 |

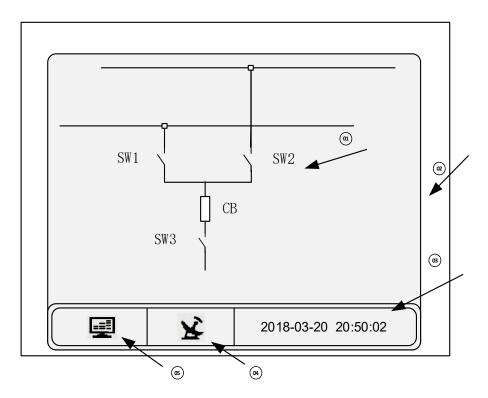

| 5.3 Apparatus Control                                                         | 247 |

| 5.4 Signaling                                                                 | 248 |

| 5.5 Event Records                                                             | 248 |

| 5.5.1 Overview                            | 248 |

|-------------------------------------------|-----|

| 5.5.2 Fault Record Events (FaultEvents)   | 248 |

| 5.5.3 Alarm Record Events                 | 249 |

| 5.5.4 Device Record                       | 249 |

| 5.5.5 Sequence of Event(SoeRecords)       | 250 |

| 5.6 Fault and Disturbance Recording       | 250 |

| 5.6.1 Wave Recording File Format          | 250 |

| 5.6.2 Fault Wave File                     | 250 |

| 5.6.3 Waveform Recording Duration         | 251 |

| 5.6.4 Fault Wave Recording                | 252 |

| 5.6.5 Logic Event Recording(EventRecords) | 252 |

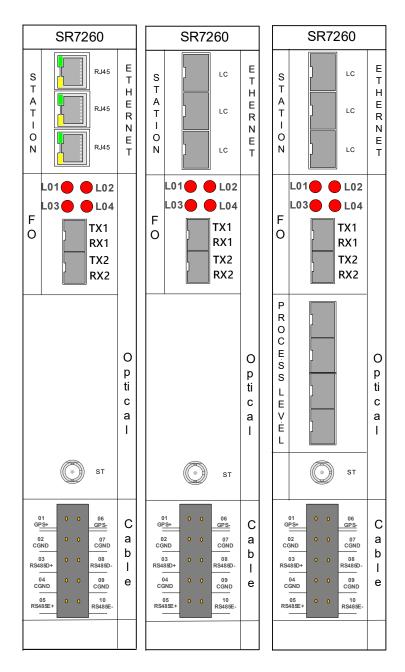

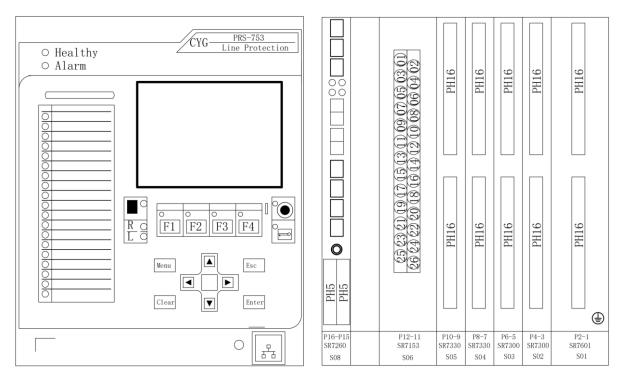

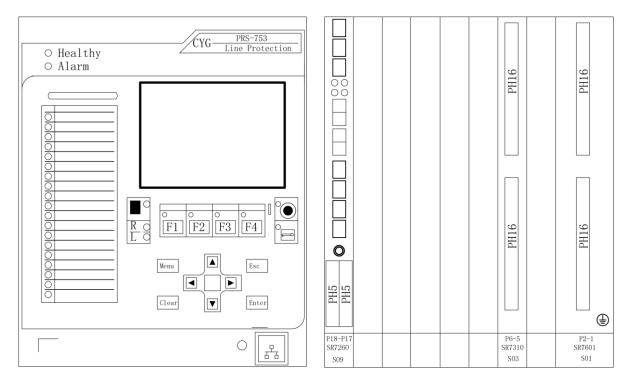

| 6 Hardware                                | 253 |

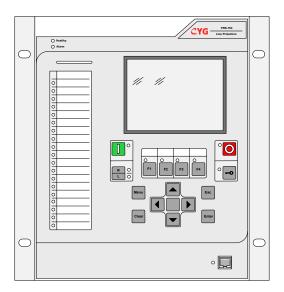

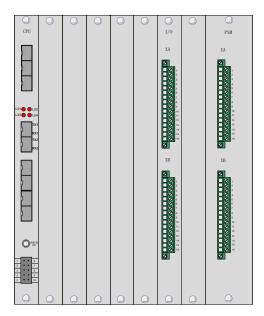

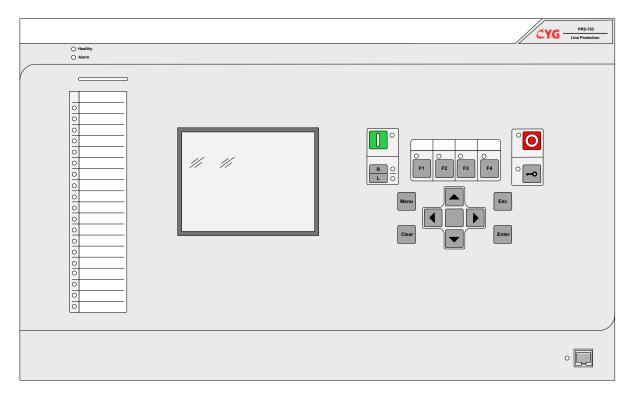

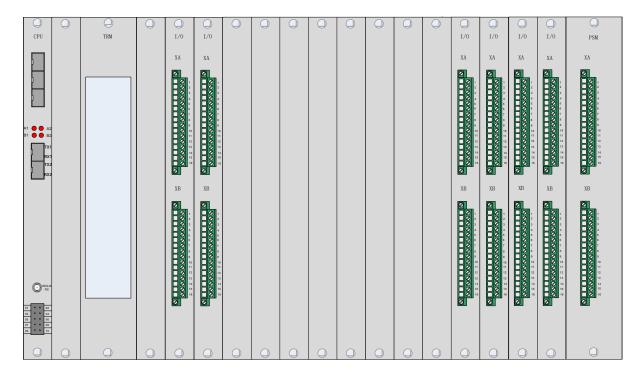

| 6.1 Overview                              | 253 |

| 6.2 Hardware Module                       | 256 |

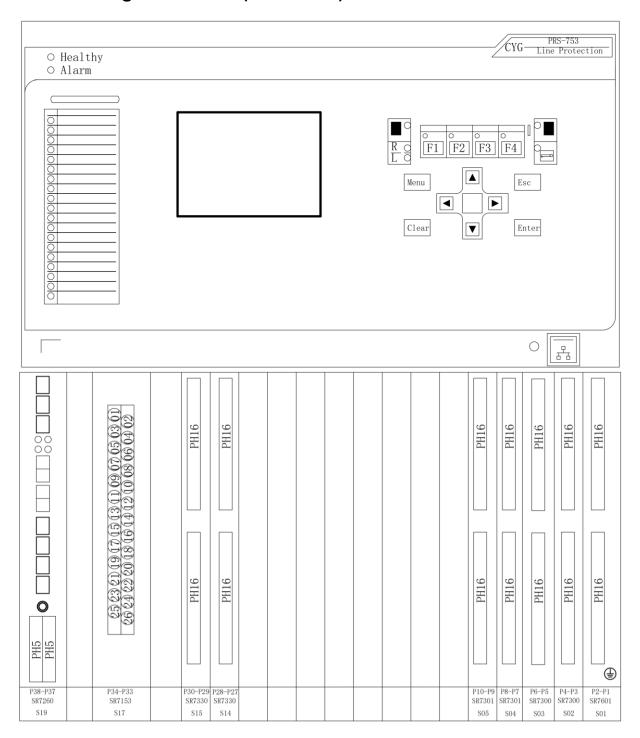

| 6.3 Human Machine Interface Module        | 256 |

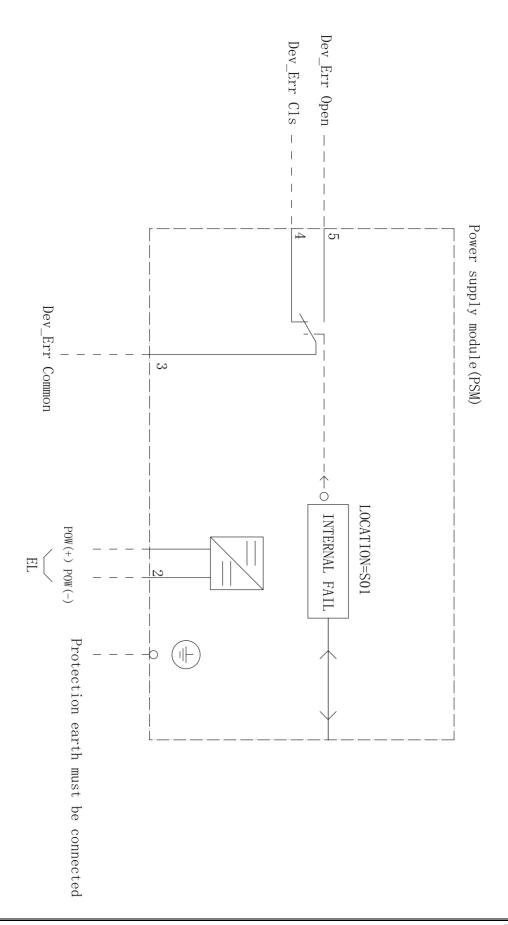

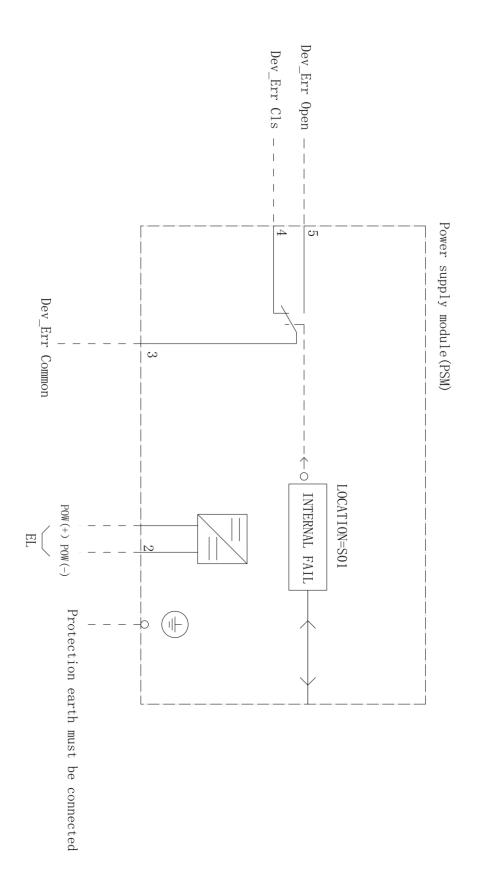

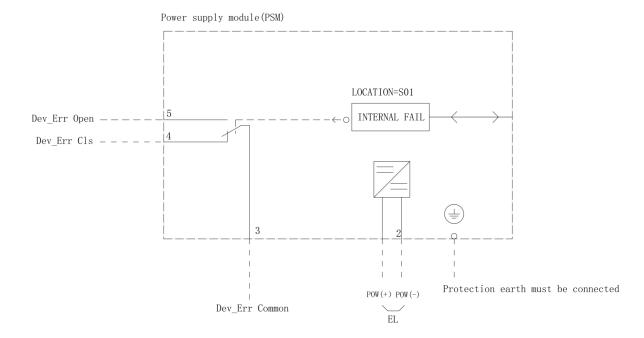

| 6.4 Power Supply Module                   | 256 |

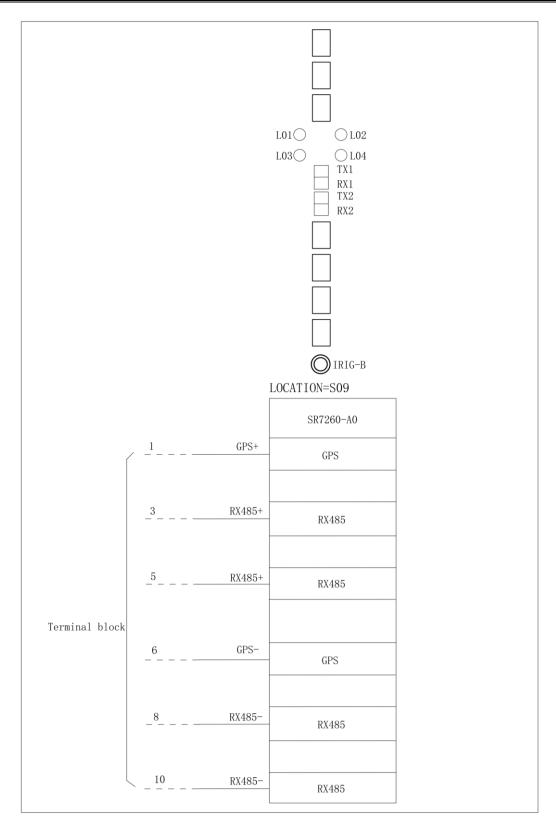

| 6.5 Main CPU Module                       | 258 |

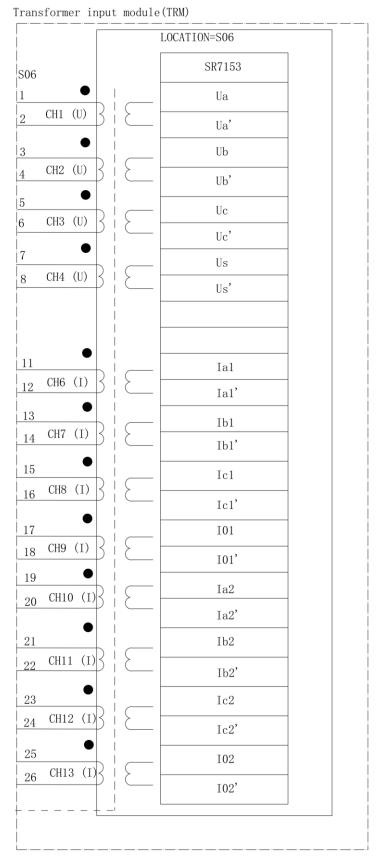

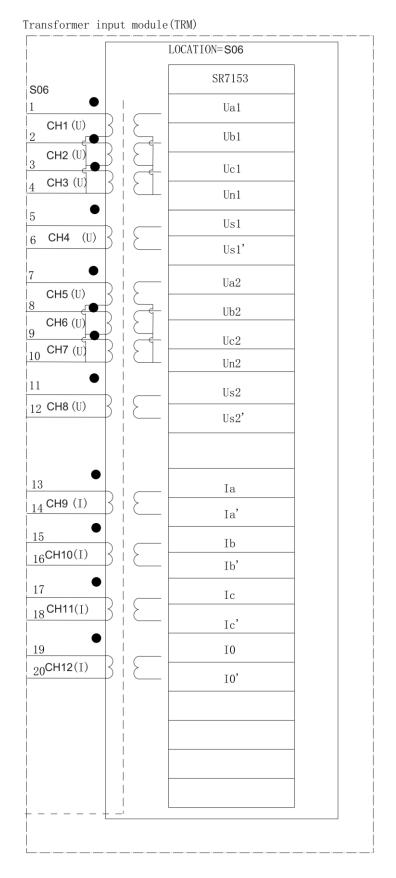

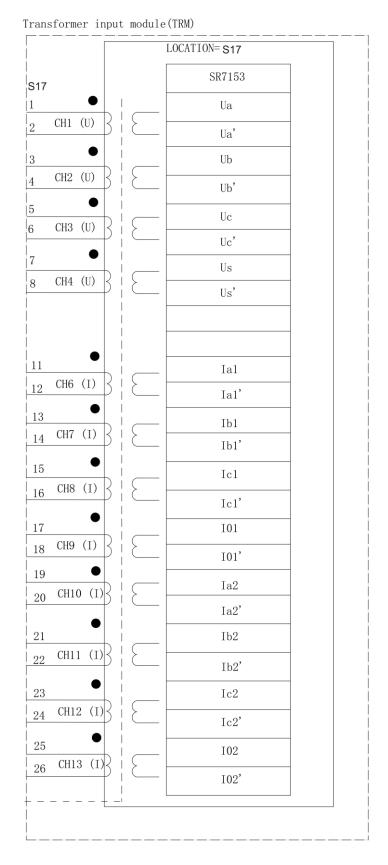

| 6.6 Transformer Module                    | 260 |

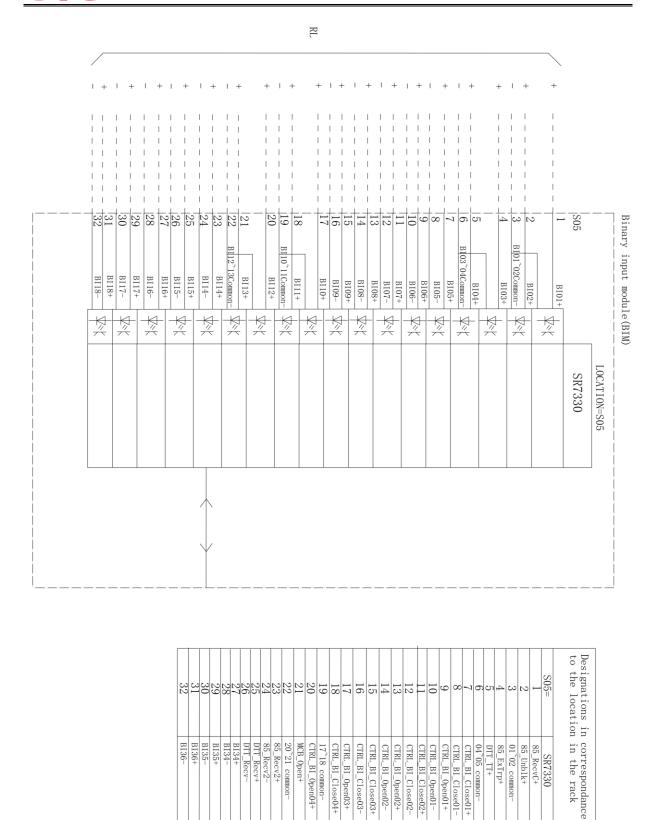

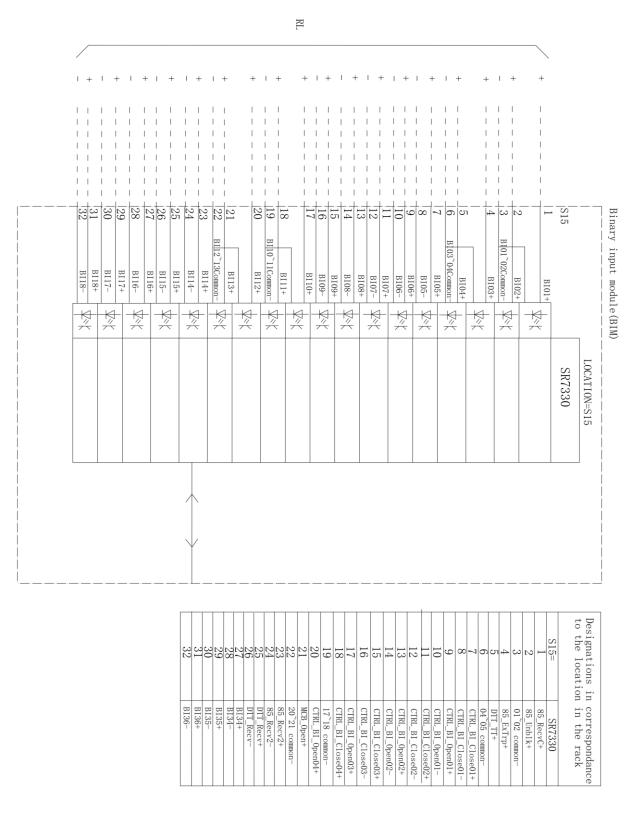

| 6.7 Binary Input Module                   | 264 |

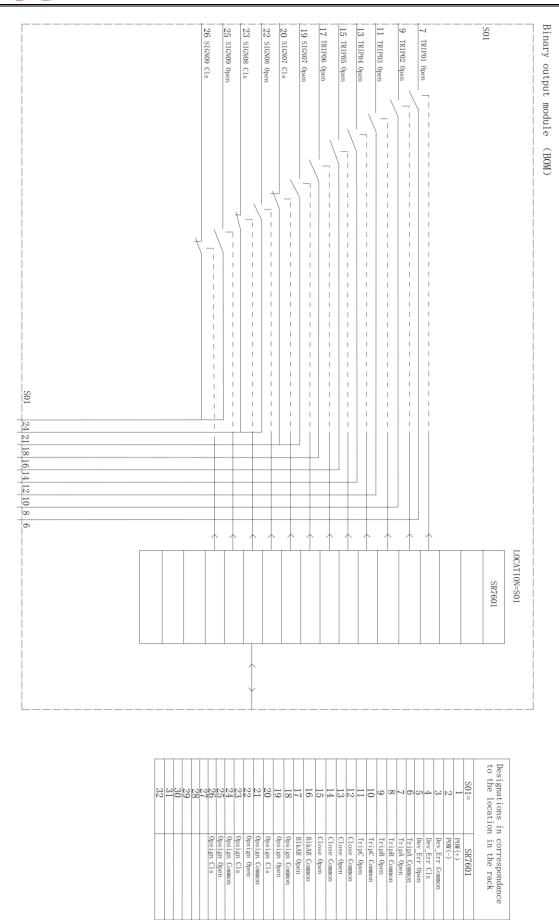

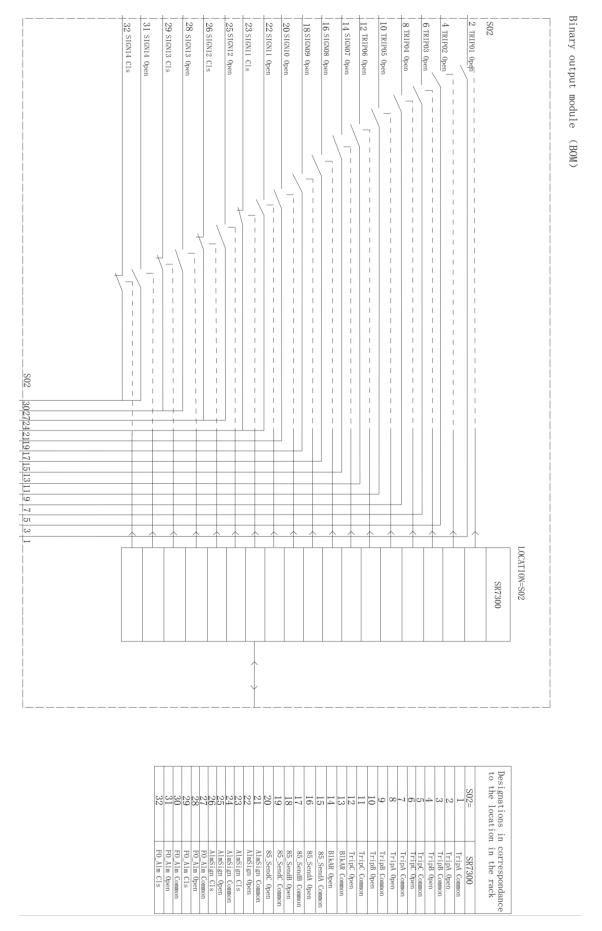

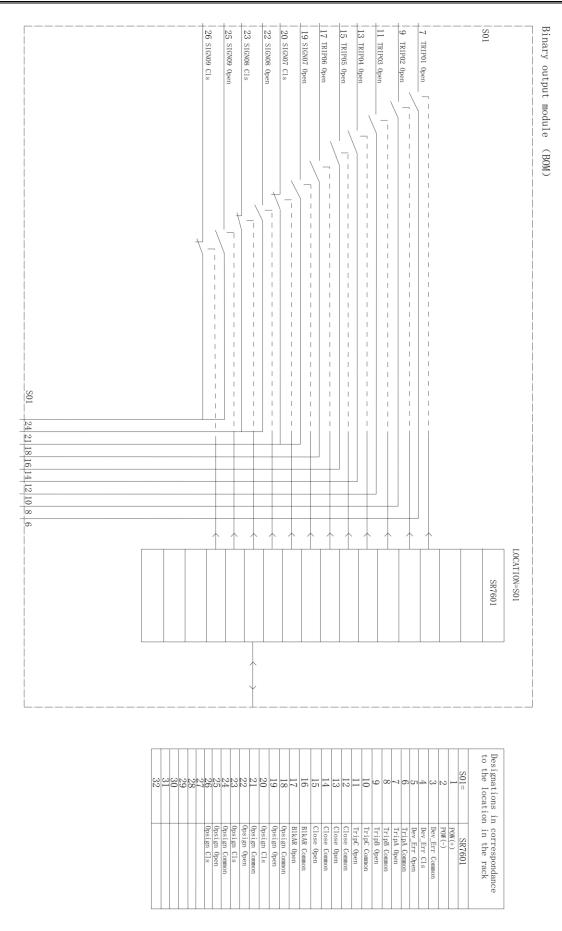

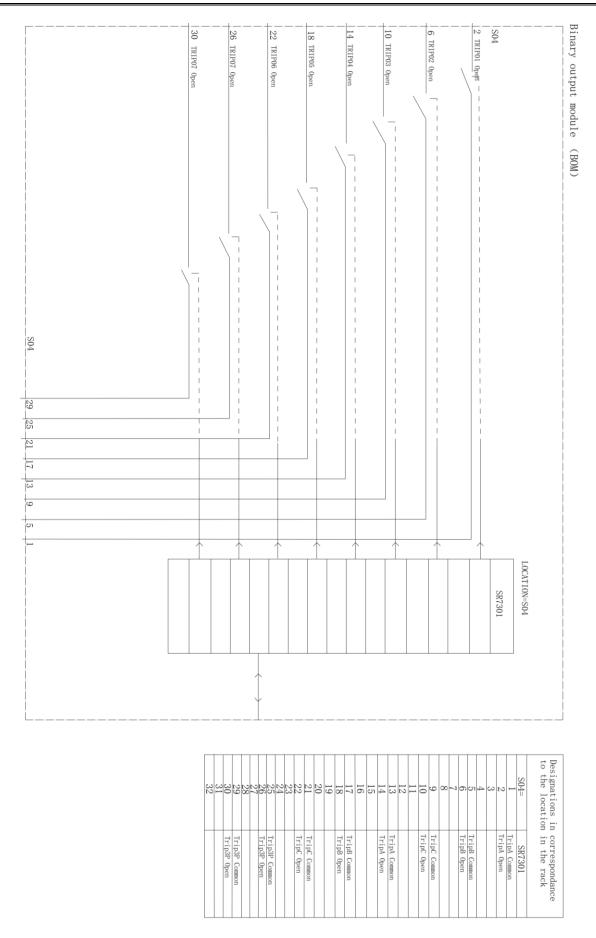

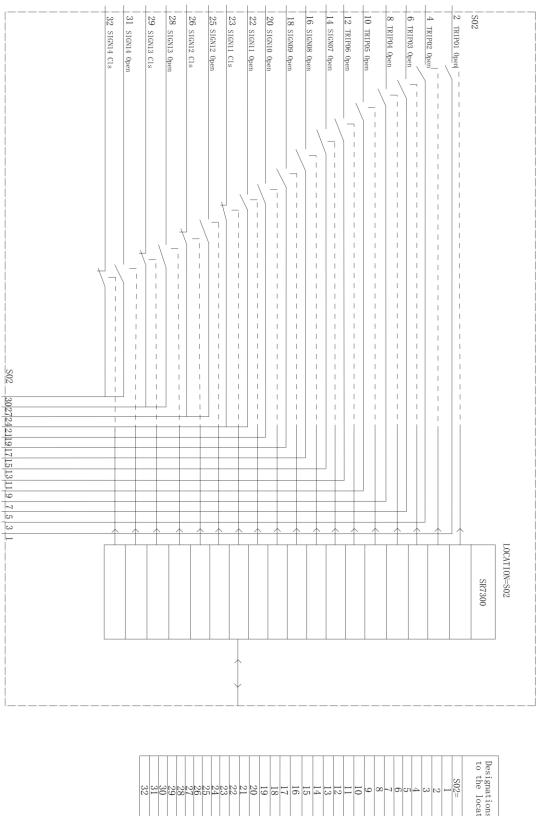

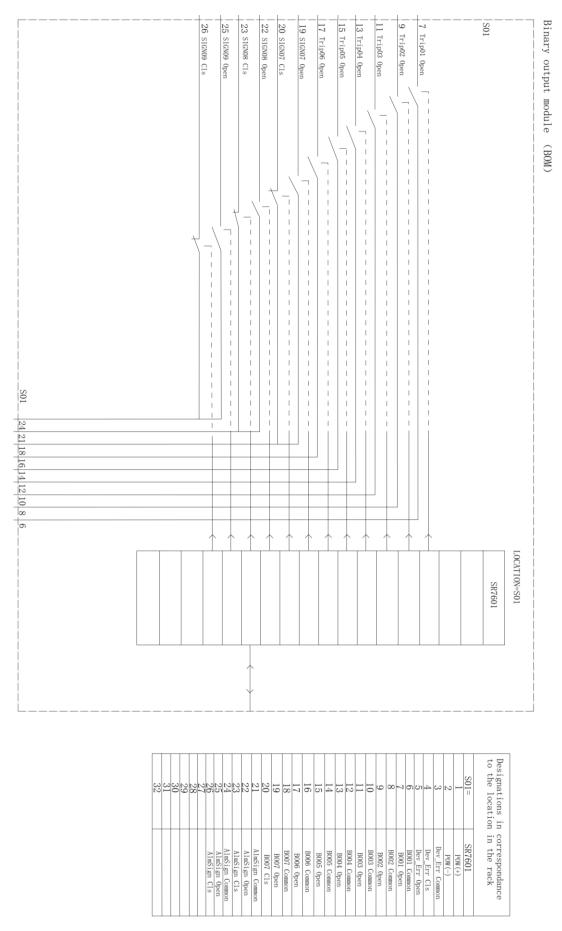

| 6.8 Binary Output Module                  | 265 |

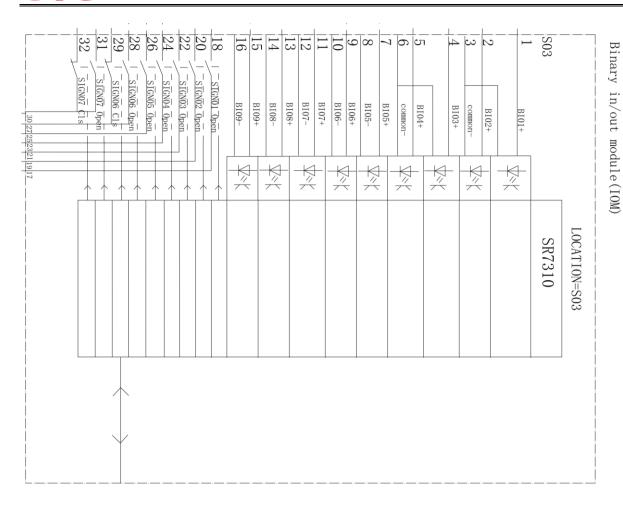

| 6.9 Binary Input/Output Module            | 267 |

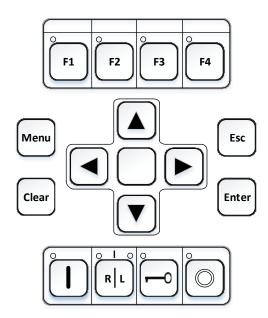

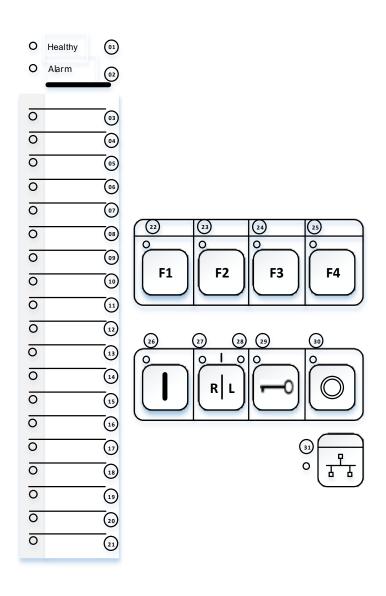

| 7 Human Machine Interface                 | 270 |

| 7.1 Overview                              | 270 |

| 7.1.1 Design Structure                    | 270 |

| 7.1.2 Function mode                       | 270 |

| 7.1.3 Operating panel keypad and keys     | 270 |

| 7.1.4 Indication of LED                   | 271 |

| 7.1.5 Configurable keys                   | 274 |

| 7.2 LCD Display description of HMI        | 274 |

| 7.2.1 Overview                            | 274 |

| 7.2.2 Normal display structure of LCD | 274 |

|---------------------------------------|-----|

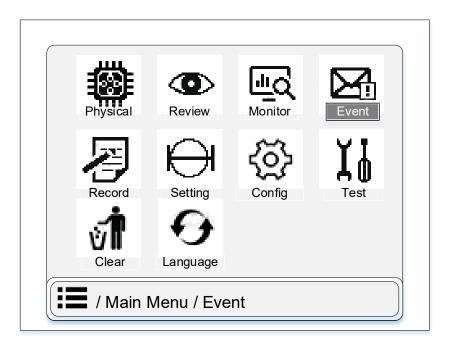

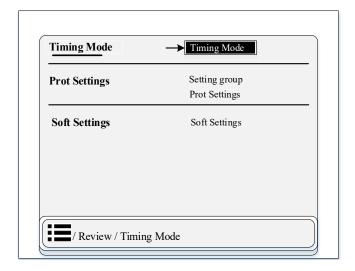

| 7.2.3 Main menu display               | 275 |

| 7.3 Sub menu functions of main menu   | 276 |

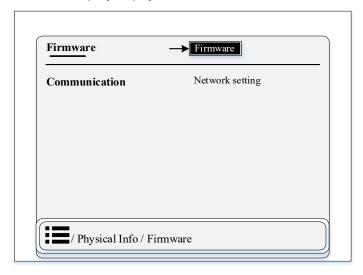

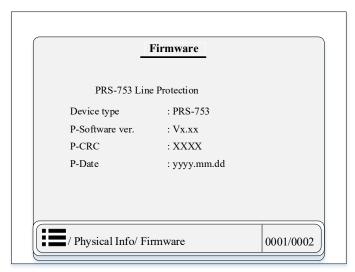

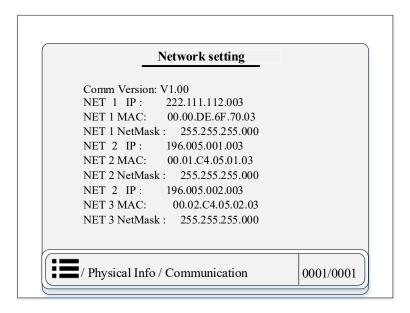

| 7.3.1 Physical Information            | 276 |

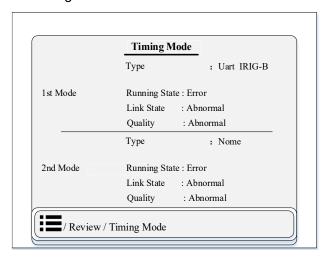

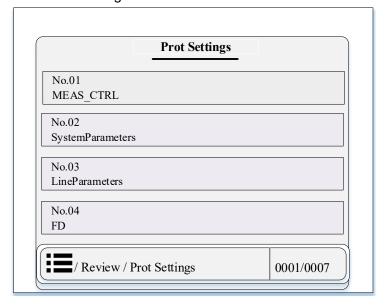

| 7.3.2 Review Information              | 279 |

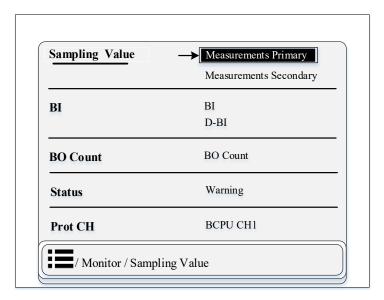

| 7.3.3 Monitoring Information          | 281 |

| 7.3.4 Event Information               | 285 |

| 7.3.5 Record Information              | 290 |

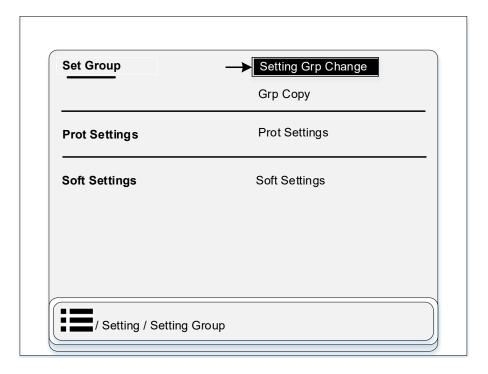

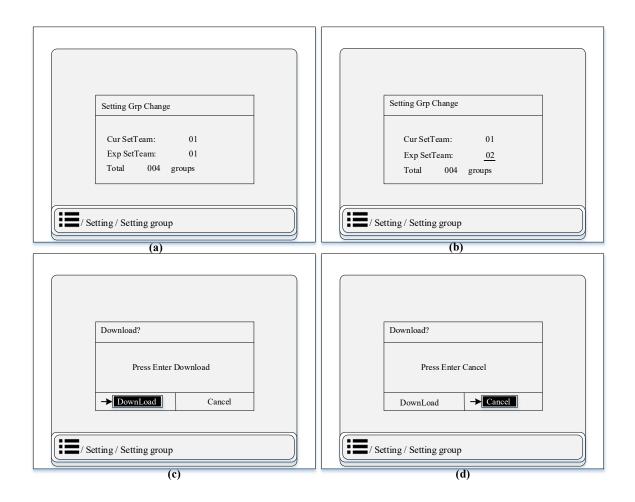

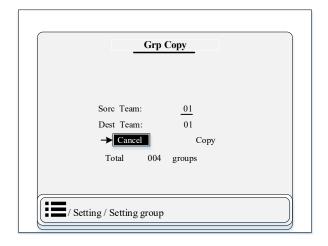

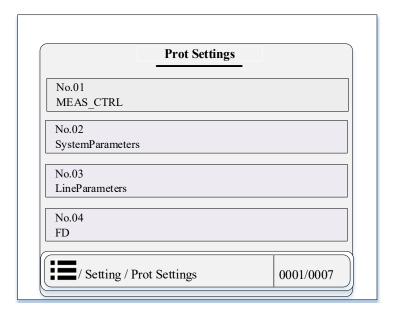

| 7.3.6 Setting Information             | 291 |

| 7.3.7 Configuration Information       | 294 |

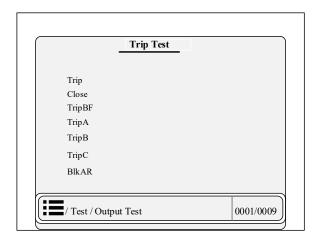

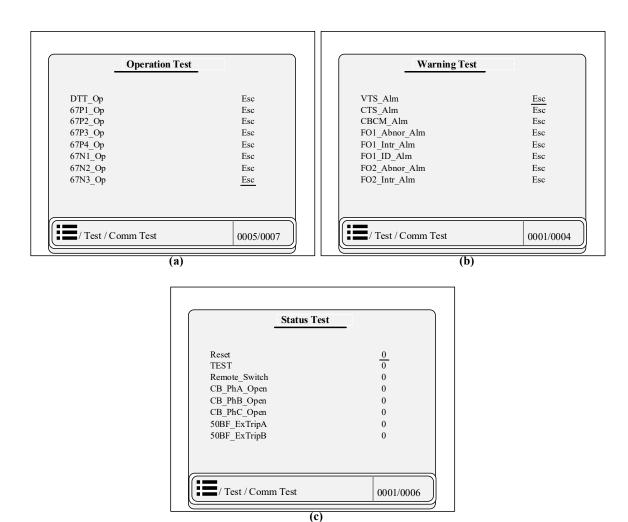

| 7.3.8 Test Information                | 297 |

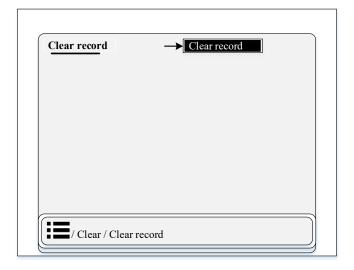

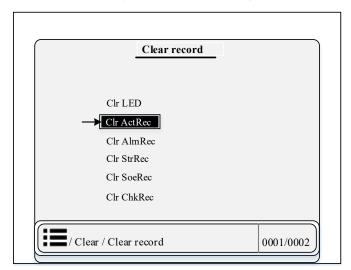

| 7.3.9 Clear Information               | 300 |

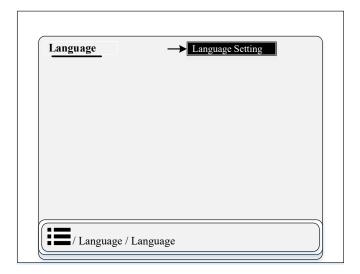

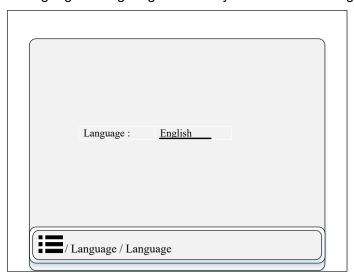

| 7.3.10 Language Information           | 301 |

| 8 Configurable Function               | 302 |

| 8.1 General Description               | 302 |

| 8.2 PRS IED Studio Software           | 302 |

| 8.3 Setting Group Selection           | 302 |

| 8.4 Configuration File Introduction   | 303 |

| 8.4.1 Parameter-PUBLIC                | 303 |

| 8.4.2 Const                           | 310 |

| 8.5 User login permissions            | 313 |

| 9 Communication Protocol              | 315 |

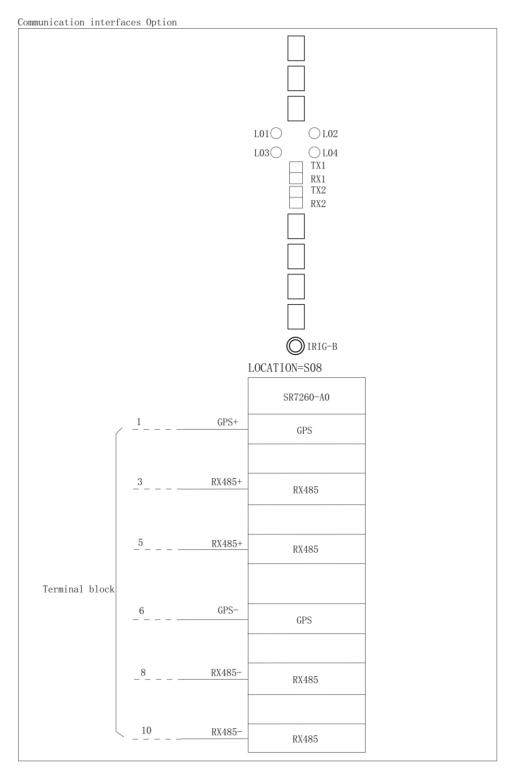

| 9.1 Overview                          | 315 |

| 9.2 Rear Communication Interface      | 315 |

| 9.2.1 Ethernet Interface              | 315 |

| 9.3 Network Topology                  | 316 |

| 9.3.1 Star Topology                   | 316 |

| 9.3.2 PRP/HSR Topology                | 316 |

| 9.4 IEC61850 Protocol                 | 316 |

| 9.4.1 Overview                        | 316 |

| 9.4.2 Communication Profiles              | 317 |

|-------------------------------------------|-----|

| 9.4.3 Data set and control block          | 320 |

| 9.4.4 Logic nodes and data modeling       | 323 |

| 9.5 DNP3.0 Protocol                       | 325 |

| 9.5.1 Overview                            | 325 |

| 9.5.2 Link Layer Functions                | 325 |

| 9.5.3 Transport Functions                 | 325 |

| 9.5.4 Application Layer Functions         | 325 |

| 9.6 IEEE 1588-2008 Protocol               | 326 |

| 9.6.1 Overview                            | 326 |

| 9.6.2 Time Synchronization                | 326 |

| 10 Commissioning                          | 327 |

| 10.1 General                              | 327 |

| 10.2 Safety Instructions                  | 327 |

| 10.2.1 Safety Identification              | 327 |

| 10.2.2 Safety Identification Examples     | 327 |

| 10.3 Commission Tools                     | 329 |

| 10.3.1 Instrumentation and Meters Notice: | 329 |

| 10.3.2 Tools Requirement:                 | 329 |

| 10.4 Commission Preparation               | 329 |

| 10.4.1 Basic Knowledge                    | 329 |

| 10.4.2 Operation Preparation              | 330 |

| 10.5 Product Checks                       | 330 |

| 10.5.1 Document Check                     | 330 |

| 10.5.2 Appearance Inspection              | 330 |

| 10.5.3 Insulation Check                   | 331 |

| 10.5.4 External Wiring Check              | 331 |

| 10.5.5 Test Category                      | 331 |

| 10.6 With the Relay Energized             | 332 |

| 10.6.1 LCD Display Check                  | 332 |

| 10.6.2 Date and Time                              | 332 |

|---------------------------------------------------|-----|

| 10.6.3 Light Emitting Diodes (LEDs)               | 332 |

| 10.6.4 Test the AC Current Circuit                | 333 |

| 10.6.5 Test the AC Voltage Inputs                 | 333 |

| 10.6.6 Test the Binary Inputs                     | 334 |

| 10.6.7 Test the Binary Onputs                     | 334 |

| 10.6.8 Protection Function Checks                 | 334 |

| 10.6.9 On-load Checks                             | 334 |

| 10.6.10 Final Checks                              | 335 |

| 11 Installation                                   | 337 |

| 11.1 General                                      | 337 |

| 11.2 Safety Instructions                          | 337 |

| 11.3 Checking the Shipment                        | 337 |

| 11.4 Material and Tools Required                  | 338 |

| 11.5 Device Location and Ambient Conditions       | 338 |

| 11.6 Mechanical Installation                      | 339 |

| 11.7 Electrical Installation and Wiring           | 341 |

| 11.7.1 TA Circuit Connection                      | 341 |

| 11.7.2 Power Supply, TV, BI and BO, Signal Wiring | 341 |

| 11.7.3 Grounding                                  | 342 |

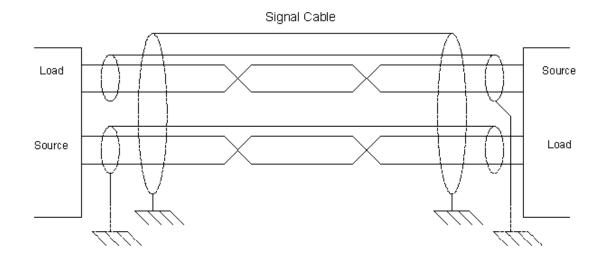

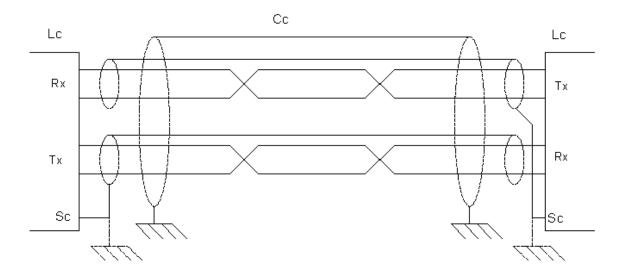

| 11.7.4 Shielded cable connection                  | 342 |

| 11.7.5 Install the optical cable                  | 342 |

| 11.7.6 Install the communication cable            | 342 |

| 11.8 Installation check                           | 343 |

| 11.8.1 Check the installation                     | 343 |

| 11.8.2 Confirm the hardware and software version  | 343 |

| 11.8.3 Device start                               | 343 |

| 12 Maintenance                                    | 345 |

| 12.1 Maintenance General                          | 345 |

| 12.2 Regular Testing                              | 345 |

| 12.3 Failure Maintenance              | 345 |

|---------------------------------------|-----|

| 12.3.1 Hardware Failure               | 345 |

| 12.3.2 Software Failure               | 346 |

| 12.4 Replace Failed Modules           | 346 |

| 13 Decommissioning and Disposal       | 347 |

| 13.1 Decommissioning                  | 347 |

| 13.1.1 Switching off                  | 347 |

| 13.1.2 Disconnecting cables           | 347 |

| 13.1.3 Dismantling                    | 347 |

| 13.2 Disposal                         | 347 |

| 14 Connection Diagrams                | 349 |

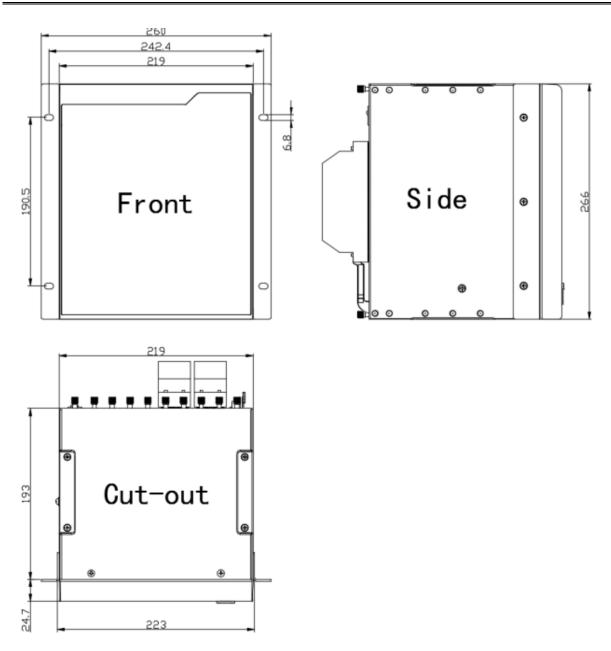

| 14.1 Drawing of structure(6U 1/2 19") | 349 |

| 14.2 Drawing of Modules(6U 1/2 19")   | 350 |

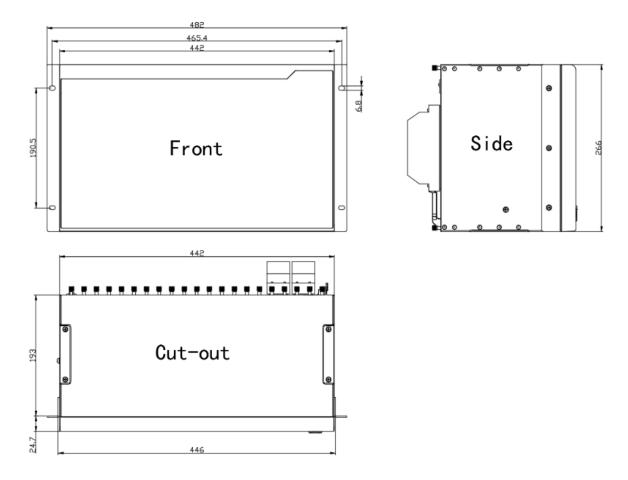

| 14.3 Drawing of structure(6U 1/1 19") | 357 |

| 14.4 Drawing of Modules(6U 1/1 19")   | 358 |

| 14.5 Drawing of structure(Digital)    | 366 |

| 14.6 Drawing of Modules(Digital)      | 366 |

| 15 Manual Version History             | 370 |

# 1 Briefly Introduction

## 1.1 Application Scope

The PRS-753 is a numerical line differential and distance protection intended for protecting and monitoring various line arrangement of various voltage level, ranging from 1000kV to 110kV. PRS-753 can detect and clear all types of internal phase-to-phase and phase-to-earth faults locating within the line protection zone.

This relay can sample the analog values from the traditional instrument transformers, or receive the sampled values from the electronic current and voltage transformers (via a merging unit). The binary inputs and outputs of this relay can be configured according to the demands of a practical engineering through the PRS IED Studio configuration tool auxiliary software, which can meet some special requirements of protection and control functions.

This relay can fully support the IEC61850 communication protocol and GOOSE function, and can completely meet the demands of a modern digitalized substation.

## 1.2 Product Function

Table 1.2-1 Functions included in the IEDs

| Description                                                       | IEC 60617 | ANSI  | CYG Code    |

|-------------------------------------------------------------------|-----------|-------|-------------|

| Line Differential Protection                                      | 3dl>L     | 87    | 87L         |

| Mho distance protection                                           | Z<        | 21    | 21M         |

| Quadrilateral distance protection,                                | Z<        | 21    | 21Q         |

| Power Swing Blocking Releasing                                    | ZPSBR     | 68    | PSBR        |

| Out-of-Step Protection                                            | ф <       | 78    | 780         |

| Scheme communication logic for distance protection                | -         | CL    | 85          |

| Scheme communication logic for directional earth fault protection | -         | CLN   | 85N         |

| Three Phase Directional Overcurrent Protection                    | 3 > ->    | 67P   | 67P(50/51P) |

| Directional Earth Fault Overcurrent Protection                    | lo>->     | 67N   | 67N(50/51N) |

| Directional Negative-sequence Overcurrent Protection              | 12>       | 6712  | 6712        |

| Breaker Failure Protection                                        | 3I>/I0>BF | 50BF  | 50BF        |

| Thermal Overload Protection                                       | 3lth>     | 49    | 49          |

| Stub Differential Protection                                      | 3I>STUB   | 50STB | 87STB       |

| Pole Discordance Protection                                       | PD        | 52PD  | 52PD        |

| Reverse Power Protection                                          | P>        | 32R   | 32R         |

| Broken Conductor Protection                                       | -         | 46BC  | 46BC        |

| Three Phase Overvoltage Protection                                | 3U>       | 59    | 59P         |

| Description                         | IEC 60617 | ANSI  | CYG Code |

|-------------------------------------|-----------|-------|----------|

| Residual Overvoltage protection     | 2(U0>)    | 59N   | 59N      |

| Three Phase Undervoltage Protection | 3U<       | 27    | 27P      |

| OverFrequency Protection            | f>        | 810   | 810      |

| UnderFrequency Protection           | f<        | 81U   | 81U      |

| Synchrocheck                        | SYNC      | 25SYN | 25SYN    |

| Automatic Reclosure                 | O ->I     | 79    | 79AR     |

| Faulty Phase Selection              | -         | 21FL  | 21FL     |

| Trip Logic                          | -         | 94    | 94T      |

| Fault Detector                      | -         | -     | FD       |

| Optical Fibre Communication         | -         | -     | FO       |

| Current circuit supervision         | -         | 87    | CTS      |

| Fuse failure supervision            | FUSEF     | 60    | VTS      |

| CB Position Supervision             | СВСМ      | CBCM  | СВСМ     |

#### 1.3 Product Features

- This device is based on a 32-bit high performance dual-core processor, internal high speed bus and intelligent I/O ports, and the hardware is in modularized design and can be configured flexibly, featuring interchangeability and easy extension and maintenance.

- Modularized hardware design makes this relay be easily upgraded or repaired by a qualified service person. Various function optional modules can satisfy various situations according to the different requirements of the users.

- The adoption of 16-bit A/D converter and the dual-channel sampling technology can ensure

the accuracy and reliability of protection sampling and the correctness of protection operation.

It also provides dedicated current transformers for metering, and ensures the high accuracy of

telemetering with 40-point high speed sampling rate per cycle.

- This device can sample the analog values from the traditional instrument transformers, or receive the sampled values from the electronic transformers. It can support the protocol IEC60044-8, IEC61850-9-2 and GOOSE.

- Various algorithms for protection and measurement have been completed in this device for the feature of electronic transformer sampling, such as the error prevention method of multialgorithms data anomaly for the digital channels, to realize high accuracy and reliability under various conditions of network faults or communication interruption.

- This device has powerful GOOSE functions, and the connection and cooperation between some devices can be realized without using electrical cables, to facilitate the realization of such functions as simple bus differential protection, overload interlock shedding function and backup automatic transfer function etc.

- This device has fully realized the technology to integrate six functions into one device: protection, measurement, control, remote signaling, merging unit function and remote module

functions, to improve the reliability.

- Various methods of GPS time synchronization are supported in this relay, including SNTP, IEEE 1588, pulse per second (PPS) and IRIG-B synchronization.

- The protection modules are completely separated from other modules, and are independent in both hardware and software. The protection functions do not depend on the communication network, so the failure of communication network will not affect the normal operation of the protection functions.

- Mature protection configuration, fast speed and high security performance can meet the

practical requirements. Each protective element is independent, so it is very convenient for

whether adopting the selected protective element.

- This device constantly measures and calculates a large amount of analog quantities, such as phase voltage, phase-to-phase voltage, neutral voltage, phase current, neutral current, active power, reactive power, power factor and frequency etc.

- The human machine interface (HMI) with a small control module (a 240×128-dot LCD, a 9-key keypad and 21 LED indicators) on the front panel is very friendly and convenient to the user.

- This device can communicate with a SAS or RTU via different communication intermediates: Ethernet network, RS-485 serial ports. The communication protocol of this device is optional: IEC61850, IEC60870-5-103, DNP3.0.

- This device can detect the tripping circuit of the circuit breaker and monitor the operation (close

or trip) time of a circuit breaker by checking the auxiliary contacts of the circuit breaker.

- Complete event recording function is provided: 512 latest fault reports, 512 latest warning records, 128 latest user operation records and 2000 latest records of time tagged sequence of event (SOE) can be recorded.

- Powerful fault and disturbance recording function is supported: 16 latest fault disturbance waves, 16 latest start disturbance waves and 4 manual disturbance waves, the duration of a wave recording is configurable.

# **2 Technical Specifications**

# 2.1 Electrical Specifications

## 2.1.1 Current Transformer Ratings

| Reference                    |              | IEC 60255-1, IEC 60255-27             |  |

|------------------------------|--------------|---------------------------------------|--|

| Rated frequency (fn)         |              | 50Hz, 60Hz                            |  |

| Nominal range                |              | fn ± 5Hz                              |  |

| Rated current (In)           |              | 1A and 5A adaptive (settable)         |  |

|                              | continuously | 3×In                                  |  |

| Thermal withstand capability | for 10s      | 20×In                                 |  |

|                              | for 1s       | 100×In                                |  |

| Burden                       |              | < 0.05VA/phase @1A, < 0.2VA/phase @5A |  |

## 2.1.2 Voltage Transformer Ratings

| Reference                    |              | IEC 60255-1, IEC 60255-27            |

|------------------------------|--------------|--------------------------------------|

| Rated frequency (fn)         |              | 50Hz, 60Hz                           |

| Nominal range                |              | fn ± 5Hz                             |

| Rated voltage (Un)           |              | 100V ~ 120V (phase-to-phase voltage) |

|                              | continuously | 240V                                 |

| Thermal withstand capability | 10s          | 360V                                 |

| 1s                           |              | 400V                                 |

| Burden at rated voltage      |              | < 0.03VA/phase @57.7V                |

## 2.1.3 Auxiliary Power Supply

| Reference                              | IEC 60255-1, IEC 60255-26                                        |                      |

|----------------------------------------|------------------------------------------------------------------|----------------------|

| Rated voltage                          | 24VDC~250VDC, 48V~250VAC                                         |                      |

| Variation                              | 80% ~ 120%                                                       |                      |

| Frequency                              | 50/60Hz, ± 5Hz                                                   |                      |

| Maximum interruption time in the       | 0%Un,100ms;                                                      |                      |

| auxiliary DC voltage without resetting | 40%Un,200ms;                                                     |                      |

| the IED                                | 70%Un,500ms                                                      |                      |

|                                        | At the Un=DC220V                                                 |                      |

| Gradual shut down / Start up           | Class C (60s shut down ramp, 5 min power off, 60s start up ramp) |                      |

| Ripple in the DC auxiliary voltage     | Class A (15% of rated @200Hz, 220VDC)                            |                      |

|                                        | 1/2 19" Case:                                                    | ≤20W (normal state), |

| Maximum load of auxiliary voltage      | 1/2 IS Case.                                                     | ≤35W (maximum state) |

| supple                                 | 1/1 19" Case:                                                    | ≤30W (normal state)  |

|                                        | i/i is Case.                                                     | ≤40W (maximum state) |

## 2.1.4 Binary Input

| Reference                         | IEC 60255-1, Clause:6.10.5 |

|-----------------------------------|----------------------------|

| Binary input number               | 1/2 19" Case:Up to 72      |

|                                   | 1/1 19" Case:Up to 108     |

| Rated voltage                     | 24VDC~250VDC               |

| Pickup voltage                    | 55% ~ 70% rated voltage    |

| "ON" value voltage                | 70% ~ 120% rated voltage   |

| "OFF" value voltage               | < 55% rated voltage        |

| Maximum permitted voltage         | 120% rated voltage         |

| Resolution of binary input signal | ≤ 1ms                      |

| Resolution of SOE                 | ≤ 1ms                      |

# 2.1.5 Binary Output

| Reference                   | IEC 60255-1              |                          |                          |

|-----------------------------|--------------------------|--------------------------|--------------------------|

| Item                        | Heavy-capacity output    | Tripping output          | Signal output            |

| Binary output               | 1/2 19" Case:Up to 30    | 1/2 19" Case:Up to 65    | 1/2 19" Case:Up to 65    |

| number                      | 1/1 19" Case:Up to 42    | 1/1 19" Case:Up to 93    | 1/1 19" Case:Up to 93    |

| Output model                | Potential-free contact   | Potential-free contact   | Potential-free contact   |

| Max system voltage          | 380Vac, 250Vdc           | 380Vac, 250Vdc           | 380Vac, 250Vdc           |

| Voltage across open contact | 1000V RMS for 1min       | 1000V RMS for 1min       | 1000V RMS for 1min       |

| Continuous                  | 10A @ 380Vac;            | 10A @ 380Vac;            | 5.0A @ 380Vac;           |

| carry                       | 10A @ 250Vd              | 10A @ 250Vd              | 5.0A @ 250Vdc            |

| Short duration              | 30A, 3s                  | 30A, 3s                  | 30A, 1s                  |

| current                     | 50A, 1s                  | 50A, 1s                  | 30A, 15                  |

|                             | 1.00A @ 48Vdc, L/R=40ms  | 1.00A @ 48Vdc, L/R=40ms  |                          |

| Breaking                    | 0.35A @ 110Vdc, L/R=40ms | 0.35A @ 110Vdc, L/R=40ms | 0.60A @ 48Vdc, L/R=40ms  |

| capacity                    | 0.30A @ 125Vdc, L/R=40ms | 0.30A @ 125Vdc, L/R=40ms | 0.10A @ 110Vdc, L/R=40ms |

| Capacity                    | 0.20A @ 220Vdc, L/R=40ms | 0.20A @ 220Vdc, L/R=40ms | 0.05A @ 220Vdc, L/R=40ms |

|                             | 0.15A @ 250Vdc, L/R=40ms | 0.15A @ 250Vdc, L/R=40ms |                          |

| Pickup time                 | < 1ms                    | < 8ms                    | < 10ms                   |

| Dropout time                | < 5ms                    | < 5ms                    | < 8ms                    |

# 2.2 Mechanical Specifications

| Mounting Way           | Flush mounted                                |  |

|------------------------|----------------------------------------------|--|

| Weight per device      | 1/2 19" Case: Approx. 8.6kg (fully equipped) |  |

|                        | 1/1 19" Case: Approx.12.5kg (fully equipped) |  |

| Mechanical size        | 1/2 19" Case: 260mm*266 mm*217.7 mm          |  |

| (width×high×deepth)    | 1/1 19" Case: 482.6mm*266 mm*217.7 mm        |  |

| Hole size (width×high) | 1/2 19" Case: 227 mm*267 mm                  |  |

|                        | 1/1 19" Case: 450 mm*267 mm                  |  |

| Display language       | Optional: Chinese, English                   |  |

| Housing material     | Metallic plates, parts and screws: Steel               |  |

|----------------------|--------------------------------------------------------|--|

|                      | Plastic parts: Polycarbonate                           |  |

| Housing color        | Silver grey                                            |  |

| Location of terminal | Rear panel of the device                               |  |

|                      | Front side:IP40 (IP52 with seal strip)                 |  |

| Protection class     | IEC60225-1: 2009 Rear side, connection terminals: IP20 |  |

|                      | Other Sides: IP40                                      |  |

# 2.3 Ambient Temperature and Humidity Range

| Standard                                | IEC 60255-1:2009                              |  |

|-----------------------------------------|-----------------------------------------------|--|

| Operating temperature range             | -40°C ~ +70°C                                 |  |

| Transport and storage temperature range | -40°C ~ +70°C                                 |  |

| Damp heat steady                        | +40°C 93%humidity 16h                         |  |

| Damp-heat test, cyclic                  | 6 cycles, +25°C to +55°C, Humidity 97% to 93% |  |

## 2.4 Communication Interfaces

## 2.4.1 Ethernet Port

| For Station Level |                   |                           |                                    |  |

|-------------------|-------------------|---------------------------|------------------------------------|--|

| Med               | Medium Parameters |                           | Parameters                         |  |

|                   |                   | Port number               | 3                                  |  |

|                   |                   | Connector type            | RJ-45                              |  |

|                   |                   | Transmission rate         | 100Mbits/s                         |  |

|                   | Electrical        | Transmission standard     | 100Base-TX                         |  |

|                   |                   | Transmission distance     | ≤ 100m                             |  |

|                   |                   | Protocol                  | IEC60870-5-103:1997, IEC61850 etc. |  |

| Ethernet:         |                   | Safety level              | Isolation to ELV level             |  |

| Electrical OR     |                   | Port number               | 3                                  |  |

| Optical           |                   | Connector type            | LC                                 |  |

|                   |                   | Transmission rate         | 100Mbits/s                         |  |

|                   | Optical           | Transmission standard     | 100Base-FX                         |  |

|                   | Optical           | Optical fiber type        | Multi-mode                         |  |

|                   |                   | Wavelength                | 1310nm                             |  |

|                   |                   | Transmission distance     | ≤ 2000m                            |  |

|                   |                   | Protocol                  | IEC60870-5-103:1997, IEC61850 etc. |  |

|                   |                   | For Process Level (If req | juired)                            |  |

| Medium            |                   |                           | Parameters                         |  |

|                   |                   |                           | 4                                  |  |

|                   |                   | Connector type            | LC                                 |  |

| Opti              | Optical           |                           | 100Mbits/s                         |  |

|                   |                   | Transmission standard     | 100Base-FX                         |  |

|                   |                   | Optical fiber type        | Multi-mode                         |  |

| Wavelength            | 1310nm  |

|-----------------------|---------|

| Transmission distance | ≤ 2000m |

## 2.4.2 Serial Port

| Medium       | Parameters            |                                  |

|--------------|-----------------------|----------------------------------|

|              | Port number           | 2                                |

|              | Baud rate             | 4800 ~ 115200bps                 |

| RS-485 (EIA) | Transmission distance | ≤ 500m @ 4800bps                 |

|              | Maximal capacity      | 32                               |

|              | Protocol              | IEC60870-5-103:1997, DNP3.0 etc. |

|              | Safety level          | Isolation to ELV level           |

## 2.4.3 Time Synchronization

| Medium           | Parameters            |                        |

|------------------|-----------------------|------------------------|

|                  | Port number           | 1                      |

|                  | Transmission distance | ≤ 500m                 |

| RS-485 (EIA)     | Maximal capacity      | 32                     |

|                  | Timing standard       | IRIG-B                 |

|                  | Safety level          | Isolation to ELV level |

|                  | Port number           | 1                      |

| Ontical Ethornot | Connector type        | ST                     |

| Optical Ethernet | Transmission distance | ≤ 2000m                |

|                  | Timing standard       | IRIG-B                 |

| IEEE 1588        | Accuracy              | ≤ 1ms                  |

## 2.4.4 Ethernet Port for Debugging

| Medium              | Parameters            |                        |

|---------------------|-----------------------|------------------------|

|                     | Port number           | 1                      |

|                     | Connector type        | RJ-45                  |

| Electrical Ethernet | Transmission rate     | 100Mbits/s             |

| (in front panel)    | Transmission standard | 100Base-TX             |

|                     | Transmission distance | ≤ 100m                 |

|                     | Safety level          | Isolation to ELV level |

# 2.5 Type Tests

## 2.5.1 Environmental Tests

| Dry heat operation test | IEC 60068-2-2,<br>IEC 60255-27 | 16h, +70℃  |

|-------------------------|--------------------------------|------------|

| Cold operation test     | IEC 60068-2-1,<br>IEC 60255-27 | 16h, -40℃  |

| Dry heat storage test   | IEC 60068-2-2,<br>IEC 60255-27 | 16h , +70℃ |

| Cold storage test           | IEC 60068-2-1,<br>IEC 60255-27 | 16h , -40℃                                                    |

|-----------------------------|--------------------------------|---------------------------------------------------------------|

|                             | IEC60255-27,                   |                                                               |

| Damp heat steady state test | Clause10.5.1.5                 |                                                               |

| +Verifcation of function &  | IEC 60255-1,                   | +40°C 93%humidity                                             |

| dielectric (10 days)        | Clause 6.12.3.6                |                                                               |

|                             | IEC 60068-2-78                 |                                                               |

| Damp host tost qualic       | IEC 60068-2-30,                | 6 cycles, $+25^{\circ}$ C to $+40^{\circ}$ C, Humidity 97% to |

| Damp-heat test, cyclic      | IEC 60255-27                   | 93%                                                           |

| Change of temperature test  | IEC 60068-2-14                 | 5 Cycles , 1°C/min, -40°C to +70°C                            |

## 2.5.2 Mechanical Tests

| Vibration response test             | IEC 60255-21-1,<br>IEC 60255-27                 | Class 1: Vibration Response: Class 1 (10-59Hz: 0.035mm, 59-150Hz: 0.5gn) |

|-------------------------------------|-------------------------------------------------|--------------------------------------------------------------------------|

| Vibration Endurance:                | IEC 60255-21-1,<br>IEC 60255-27                 | Class 1 (10-150Hz: 1gn)                                                  |

| Shock Response                      | IEC 60255-21-2,<br>IEC 60255-27                 | Class 1 (5gn)                                                            |

| Shock Withstands                    | IEC 60255-21-2,<br>IEC 60255-27                 | Class 1 (15gn)                                                           |

| Bump                                | IEC 60255-21-2,<br>IEC 60255-27                 | Class 1(10gn)                                                            |

| Seismic<br>+Verifcation of function | IEC 60255-21-3<br>IEC 60255-1,<br>Clause 6.13.3 | Class I                                                                  |

## 2.5.3 Electrical Tests

| Impulse Voltage Tests.        | IEC 60255-27 | Impulse test: 5kV (rated insulation voltage ≤ 63V);Impulse test: 1kV (rated insulation voltage > 63V); |

|-------------------------------|--------------|--------------------------------------------------------------------------------------------------------|

| AC or DC Dielectric Test      | IEC 60255-27 | dielectric 50,60Hz 5/60s DC 2.8KV AC 2KV                                                               |

| Insulation Resistance         | IEC 60255-27 | >100Mohm @500Vdc                                                                                       |

| Protective Bonding Resistance | IEC 60255-27 | Test current DC20A, >12 Vac /Vdc, >60s,< 0.1 ohm                                                       |

# 2.5.4 Electromagnetic Compatibility

| Burst Disturbance Test / Damped Oscillatory Wave Immunity Test                          | IEC 60255-26,<br>IEC 61000-4-18 | For Power Supply, Binary Input / Output:Common Mode: 2.5kV, Differential Mode: 1kV;For Communication Port:Common Mode: 1kV                                                                                     |

|-----------------------------------------------------------------------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Electrostatic Discharge test                                                            | IEC 60255-26,<br>IEC 61000-4-2  | Contact Discharge: 8kV, Air Discharge: 15kV                                                                                                                                                                    |

| Fast Transient test                                                                     | IEC 60255-26,<br>IEC 61000-4-4  | (Power / Earth Port: 4kV, Signal / Control Port: 2kV)                                                                                                                                                          |

| Surge Immunity Test                                                                     | IEC 60255-26,<br>IEC 61000-4-5  | For Power Supply, Binary Input / Output: L-E: 4kV, L-L: 2kV, voltage waveform: 1.2/50µs, current waveform: 8/20µs; Communication Port: L-E: 1kV, L-L: -, voltage waveform: 1.2/50µs, current waveform: 8/20µs) |

| Conducted radio interference test                                                       | IEC 60255-26,<br>IEC 61000-4-6  | 150kHz~80MHz(Uo: 140dB μV or Uo: 10V)                                                                                                                                                                          |

| Electromagnetic fields immunity                                                         | IEC 60255-26,<br>IEC 61000-4-3  | Test Field Strength: 10V/m , Sweep frequency: 80MHz - 1000MHz, Spot frequency: 80MHz, 160MHz, 450MHz, 900MHz @ 80% Modulation & Pulse                                                                          |

| immunity to conduct,<br>common mode disturbance<br>in frequency range 0 Hz to<br>150KHz | 61000-4-16                      | Level 4: continuous 30V,short duration 300V at 50/3,50,60Hz; 15Hz~150Hz:30-3 decreases at 20dB/decade; 150Hz~1.5kHz:3 constant; 1.5kHz~15kHz:3-30 increases at 20dB/decade; 15kHz~150kHz:30 constant           |

| Power frequency magnetic fields                                                         | IEC 61000-4-8,<br>IEC 60255-26  | Continuous: 100A/m, Short Duration 1s to 3s: 1000A/m)                                                                                                                                                          |

| Pulse magnetic field immunity test                                                      | IEC 61000-4-9                   | Class 5: Current 6.4/16µs, 1000A/m                                                                                                                                                                             |

| Damped oscillatory magnetic field immunity test                                         | IEC 61000-4-10                  | Class 5: 0.1MHz&1MHz, 100A/m                                                                                                                                                                                   |

| Power frequency immunity tests                                                          | IEC 60255-26                    | Input: Class A,Common Mode: 300V, Differential Mode: 150V                                                                                                                                                      |

| Ring wave immunity test                             | IEC 61000-4-12         | Ring Wave Class 4,4kV                                                                                                                                                                     |

|-----------------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Conducted RF interference on power supply terminals | IEC 60255-26, CISPR 22 | Conducted Emission Limit for Auxiliary Power Supply Port: Frequency range: 0.15MHz - 0.5MHz (Quasi Peak: 79μV, Avg: 66μV), Frequency range: 0.5MHz - 30MHz (Quasi Peak: 73μV, Avg: 60μV); |

| Radiated interference                               | IEC 60255-26, CISPR 22 | Radiated Emission Limit on Enclosure Port : Frequency range: 30MHz - 230MHz (Quasi Peak: 40μV), Frequency range: 230MHz - 1000MHz (Quasi Peak: 47μV)                                      |

## 2.6 Terminals

| Connection Type              | Wire Size                    |

|------------------------------|------------------------------|

| CT and VT circuit connectors | Screw terminals,4mm² lead    |

| Binary I/O connection system | Screw terminals, 2.5mm² lead |

## 2.7 Measurement Range and Accuracy

| Metering Item                  | Range                                                                             | Accuracy                   |

|--------------------------------|-----------------------------------------------------------------------------------|----------------------------|

| Phase range                    | 0° ~ 360°                                                                         | ≤ 0.5% or ±1°              |

| Frequency                      | 35.00Hz ~ 70.00Hz                                                                 | ≤ 0.01Hz                   |

| Current                        | 0.051544.0015                                                                     | ±0.5%ln, 0.05ln~1.00ln     |

| (three phase 3lp)              | 0.05ln <l<4.00ln< td=""><td><math>\pm</math>0.5%l, 1.00ln~4.00ln</td></l<4.00ln<> | $\pm$ 0.5%l, 1.00ln~4.00ln |

| Voltage                        | 0.05115-411-4 50115                                                               | ±0.5%Un, 0.05Un~1.00Un;    |

| (Phase 3Up, Phase-to-Phase 3Up | 0.05Un <u<1.50un<br>p)</u<1.50un<br>                                              | ±0.5%U, 1.00Un~1.50Un      |

## 2.8 Protective Functions

## 2.8.1 Fault Detector

## 2.8.1.1 Superimposed Current Element

| Accuracy | ≤ 2.5% Setting or 0.02In, whichever is greater |

|----------|------------------------------------------------|

|----------|------------------------------------------------|

## 2.8.1.2 Residual Current Element

## 2.8.2 Line Differential Protection

| Accuracy ≤ 2.5% Setting or 0.02In, whichever is greater |

|---------------------------------------------------------|

|---------------------------------------------------------|

| Time delay accuracy | ≤ 25ms (at 4 times current setting) |

|---------------------|-------------------------------------|

## 2.8.3 Distance Protection

| Accuracy            | $\leq$ 2.5% Setting or 0.1 $\Omega$ /ln, whichever is greater |

|---------------------|---------------------------------------------------------------|

| Time delay accuracy | ≤ 1% Setting+25ms                                             |

## 2.8.4 Three Phase Directional Overcurrent Protection

| Accuracy                                           | ≤ 2.5% Setting or 0.02In, whichever is greater      |

|----------------------------------------------------|-----------------------------------------------------|

| Resetting ratio                                    | 97%                                                 |

| Time delay accuracy (definite-time characteristic) | ≤ 1% Setting+30ms (at 2 times current setting)      |

| Time delay accuracy (inverse-time characteristic)  | $\leq$ 2.5% of operating time or 30ms, whichever is |

|                                                    | greater (start value multiples in range of 1.220    |

|                                                    | when I> In)                                         |

|                                                    | $\leq$ 5.0% of operating time or 40ms, whichever is |

|                                                    | greater (start value multiples in range of 220      |

|                                                    | when l≤ ln)                                         |

## 2.8.5 Directional Earth Fault Protection

| Accuracy                                           | ≤ 2.5% Setting or 0.02In, whichever is greater      |

|----------------------------------------------------|-----------------------------------------------------|

| Resetting ratio                                    | 97%                                                 |

| Time delay accuracy (definite-time characteristic) | ≤ 1% Setting+30ms (at 2 times current setting)      |

| Time delay accuracy (inverse-time characteristic)  | $\leq$ 2.5% of operating time or 30ms, whichever is |

|                                                    | greater (start value multiples in range of 1.220    |

|                                                    | when I> In)                                         |

|                                                    | $\leq$ 5.0% of operating time or 40ms, whichever is |

|                                                    | greater (start value multiples in range of 220      |

|                                                    | when l≤ ln)                                         |

## 2.8.6 Directional Negative-sequence Overcurrent Protection

| Accuracy                                           | ≤ 2.5% Setting or 0.02In, whichever is greater      |

|----------------------------------------------------|-----------------------------------------------------|

| Resetting ratio                                    | 97%                                                 |

| Time delay accuracy (definite-time characteristic) | ≤ 1% Setting+30ms (at 2 times current setting)      |

| Time delay accuracy (inverse-time characteristic)  | $\leq$ 2.5% of operating time or 30ms, whichever is |

|                                                    | greater (start value multiples in range of 1.220    |

|                                                    | when I> In)                                         |

|                                                    | $\leq$ 5.0% of operating time or 40ms, whichever is |

|                                                    | greater (start value multiples in range of 220      |

|                                                    | when l≤ ln)                                         |

## 2.8.7 Breaker Failure Protection

| Accuracy            | ≤ 2.5% Setting or 0.02In, whichever is greater |

|---------------------|------------------------------------------------|

| Time delay accuracy | ≤ 1% Setting+20ms (at 2 times current setting) |

| Drop-off time       | ≤ 12.5ms                                       |

## 2.8.8 Thermal Overload Protection

| Accuracy            | ≤ 2.5% Setting or 0.02In, whichever is greater      |

|---------------------|-----------------------------------------------------|

| Resetting ratio     | 97%                                                 |

| Time delay accuracy | $\leq$ 2.5% of operating time or 30ms, whichever is |

|                     | greater (start value multiples in range of 1.220    |

|                     | when I> In)                                         |

|                     | $\leq$ 5.0% of operating time or 40ms, whichever is |

|                     | greater (start value multiples in range of 220      |

|                     | when l≤ ln)                                         |

## 2.8.9 Stub Differential Protection

| Accuracy            | ≤ 2.5% Setting or 0.02In, whichever is greater |

|---------------------|------------------------------------------------|

| Resetting ratio     | 97%                                            |

| Time delay accuracy | ≤ 1% Setting+30ms (at 2 times current setting) |

## 2.8.10 Pole Discordance Protection

| Accuracy            | ≤ 2.5% Setting or 0.02In, whichever is greater |

|---------------------|------------------------------------------------|

| Resetting ratio     | 97%                                            |

| Time delay accuracy | ≤ 1% Setting+30ms (at 2 times current setting) |

## 2.8.11 Reverse Power Protection

| Accuracy            | ≤ 2.5% Setting or 0.5W, whichever is greater |  |

|---------------------|----------------------------------------------|--|

| Resetting ratio     | 97%                                          |  |

| Time delay accuracy | ≤ 1% Setting+30ms                            |  |

## 2.8.12 Broken Conductor Protection

| Accuracy            | ≤ 2.5% Setting    |  |

|---------------------|-------------------|--|

| Resetting ratio     | 97%               |  |

| Time delay accuracy | ≤ 1% Setting+30ms |  |

## 2.8.13 Three Phase Overvoltage Protection

| Accuracy                                           | $\leq$ 2.5% Setting or 0.01Un, whichever is greater |  |

|----------------------------------------------------|-----------------------------------------------------|--|

| Resetting ratio                                    | 98%                                                 |  |

| Time delay accuracy (definite-time characteristic) | ≤ 1% Setting+30ms (at 1.2 times voltage setting)    |  |

| Time delay accuracy (inverse-time characteristic)  | $\leq$ 2.5% of operating time or 30ms, whichever is |  |

|                                                    | greater (for voltage between 1.2 and 2 multiples of |  |

|                                                    | pickup)                                             |  |

## 2.8.14 Residual Overvoltage Protection

| Accuracy                                           | ≤ 2.5% Setting or 0.01Un, whichever is greater  |  |

|----------------------------------------------------|-------------------------------------------------|--|

| Resetting ratio                                    | 98%                                             |  |

| Time delay accuracy (definite-time characteristic) | ≤ 1% Setting+30ms (at 1.2 times voltage setting |  |

|                                                   | $\leq$ 2.5% of operating time or 30ms, whichever is |

|---------------------------------------------------|-----------------------------------------------------|

| Time delay accuracy (inverse-time characteristic) | greater (for voltage between 1.2 and 2 multiples of |

|                                                   | pickup)                                             |

## 2.8.15 Three Phase Undervoltage Protection

| Accuracy                                           | ≤ 2.5% Setting or 0.01Un, whichever is greater      |  |

|----------------------------------------------------|-----------------------------------------------------|--|

| Resetting ratio                                    | 102%                                                |  |

| Time delay accuracy (definite-time characteristic) | ≤ 1% Setting+30ms (at 0.8 times voltage setting)    |  |

|                                                    | $\leq$ 2.5% of operating time or 30ms, whichever is |  |

| Time delay accuracy (inverse-time characteristic)  | greater (for voltage between 0.5 and 0.8 multiples  |  |

|                                                    | of pickup)                                          |  |

## 2.8.16 Overfrequency Protection

| Accuracy            | ≤ 0.02Hz                                          |

|---------------------|---------------------------------------------------|

| Time delay accuracy | ≤1% Setting+30ms (at 1.2 times frequency setting) |

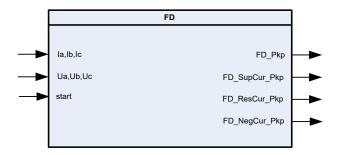

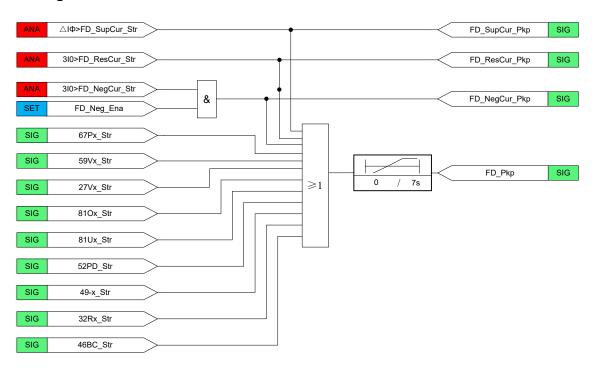

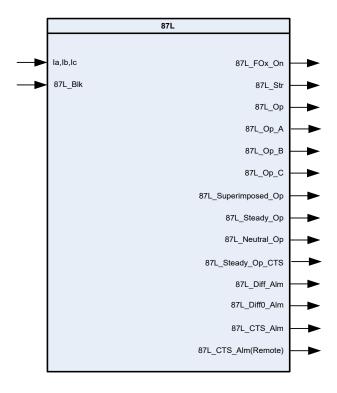

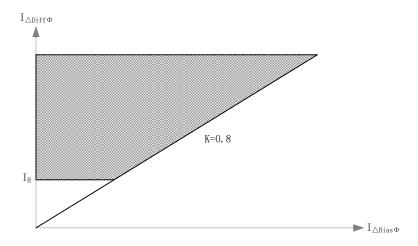

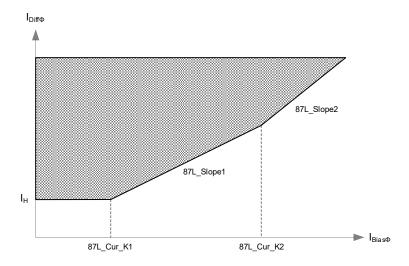

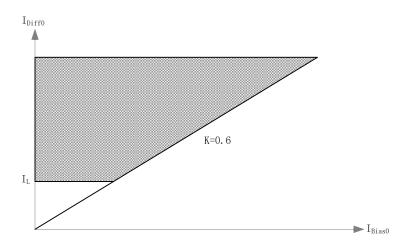

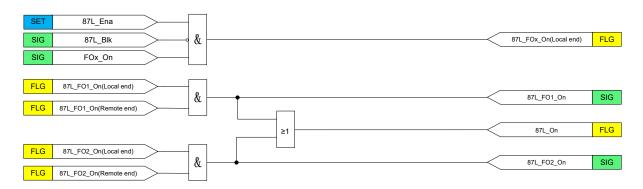

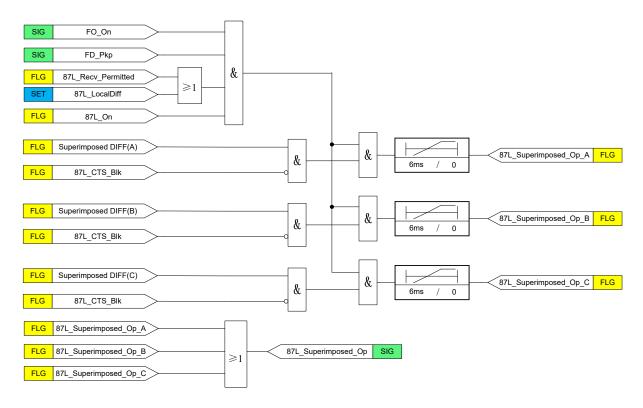

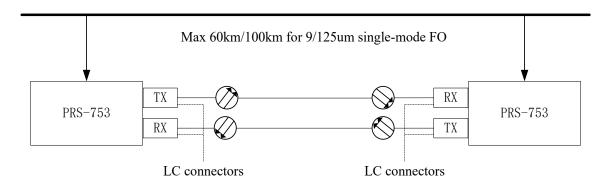

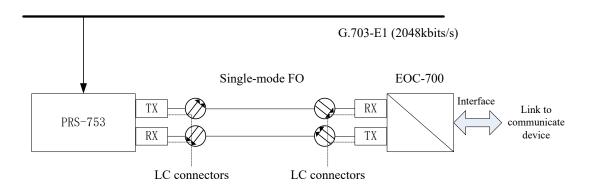

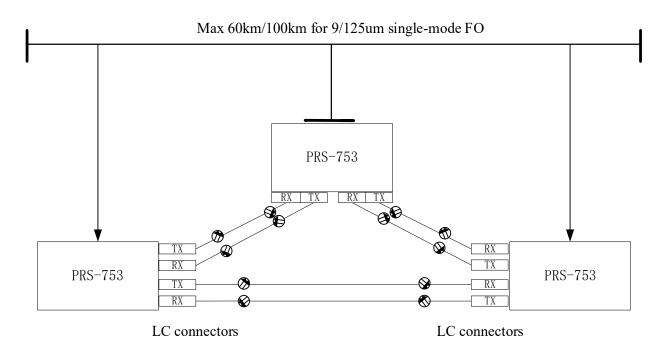

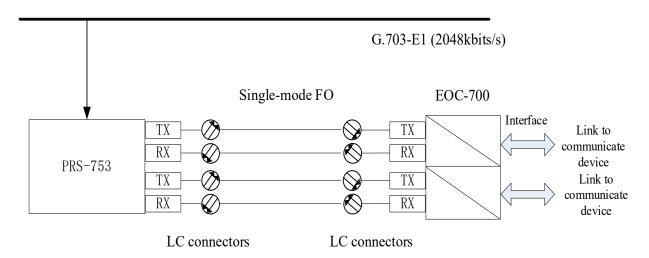

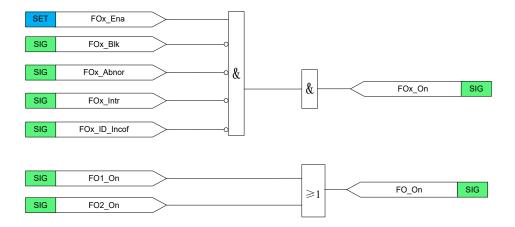

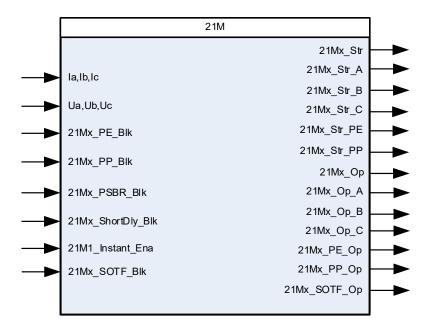

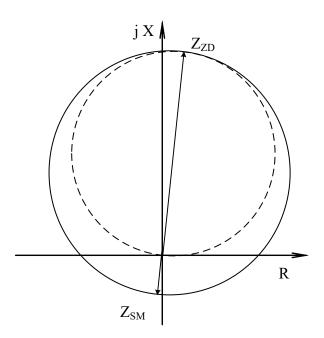

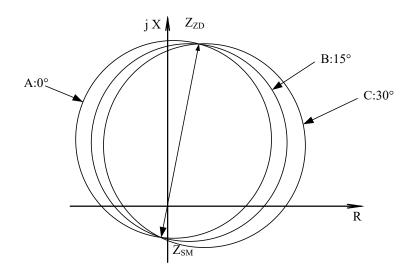

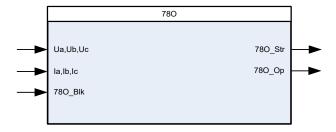

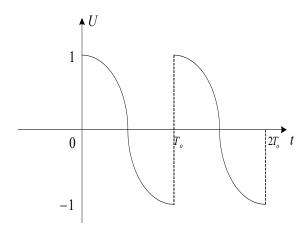

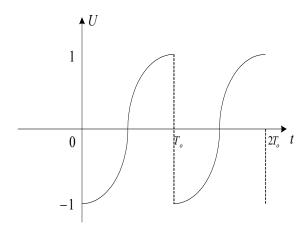

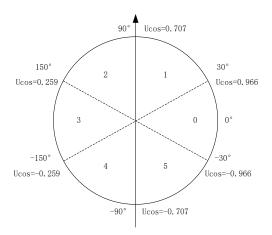

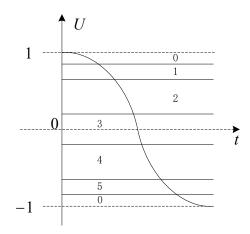

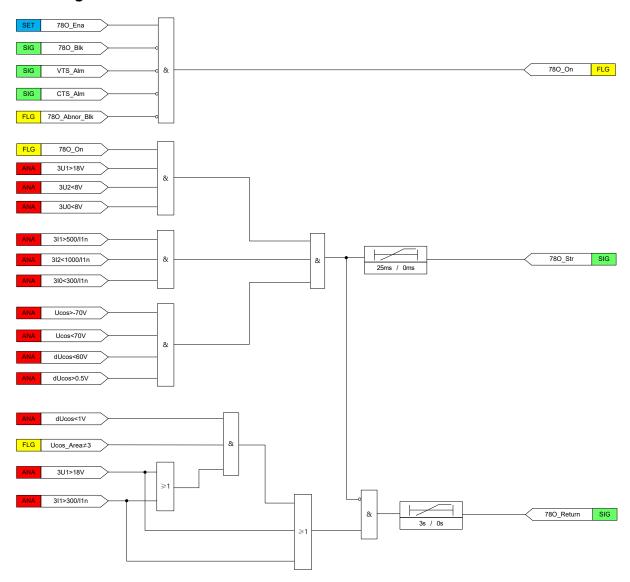

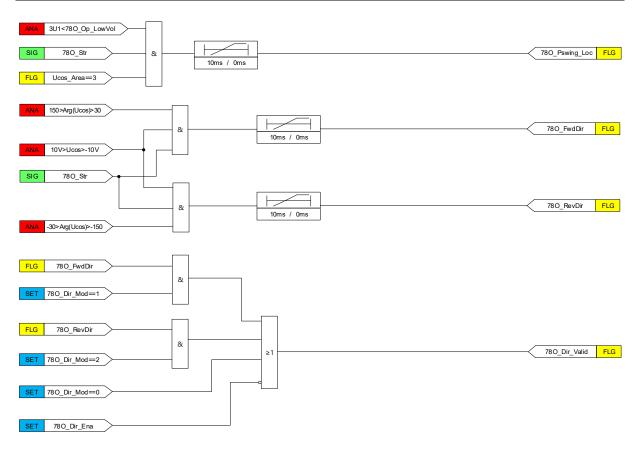

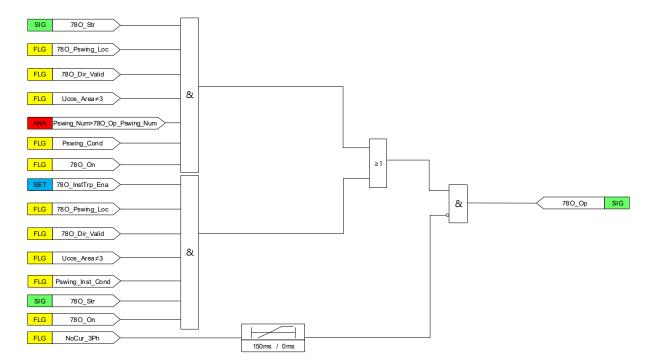

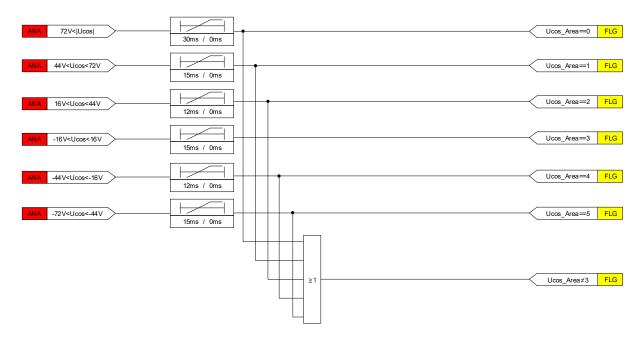

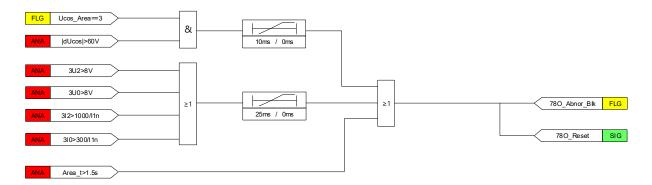

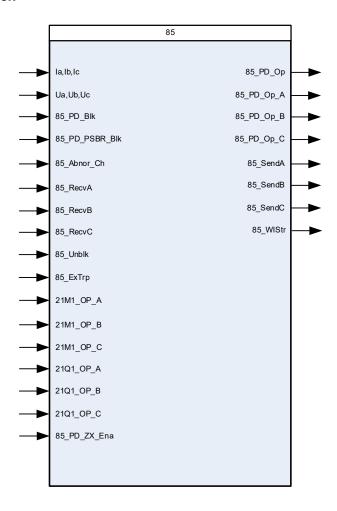

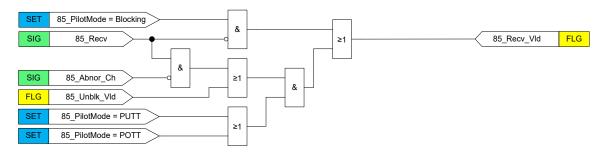

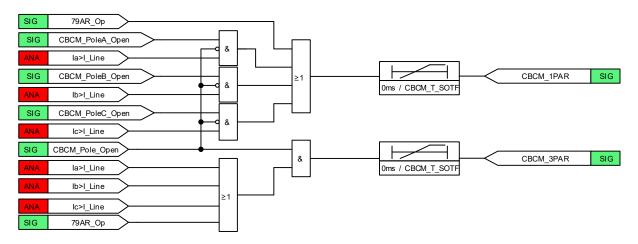

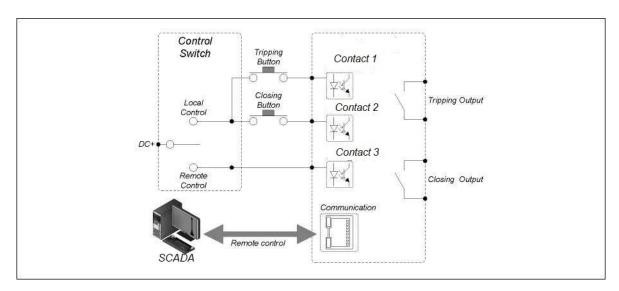

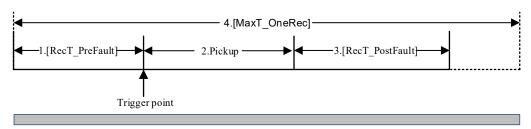

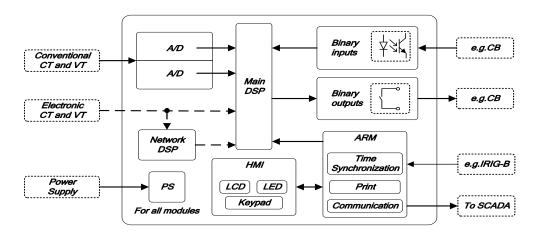

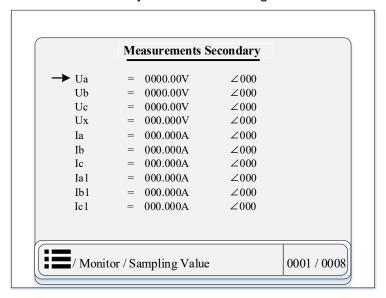

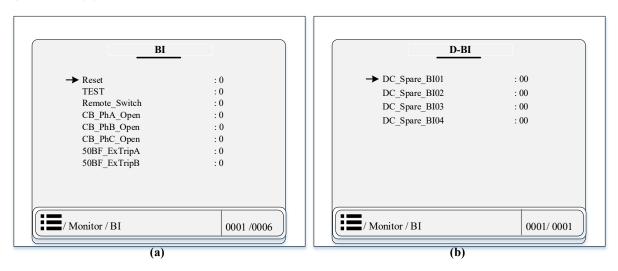

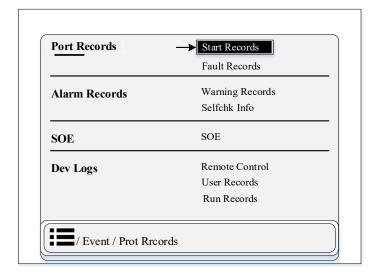

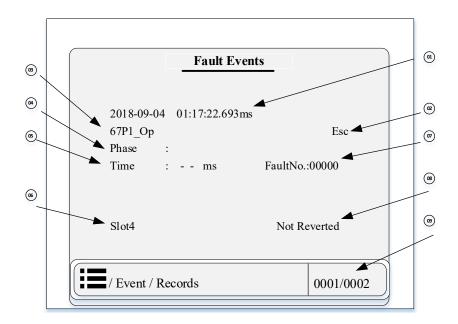

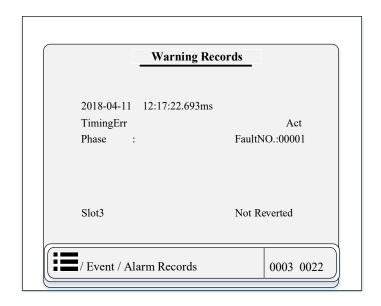

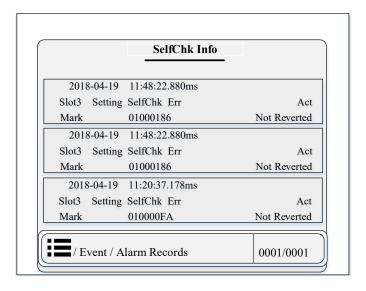

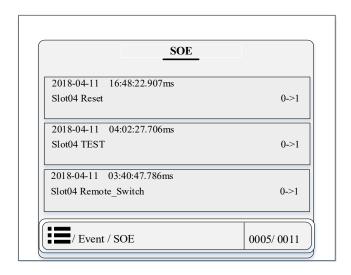

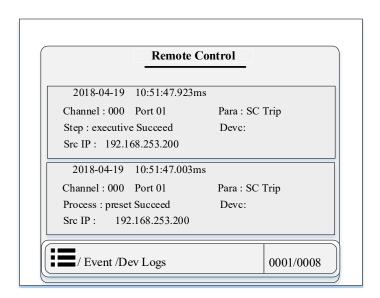

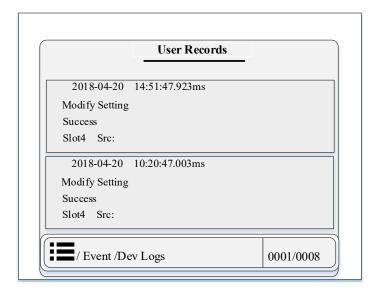

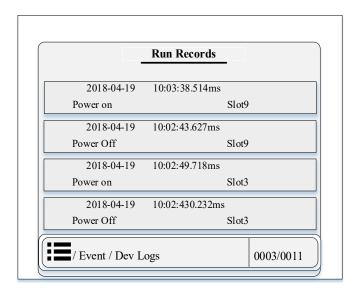

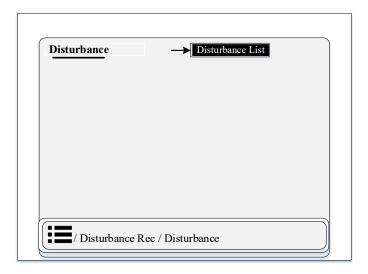

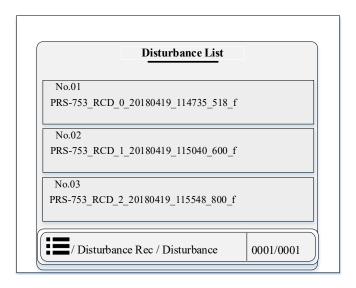

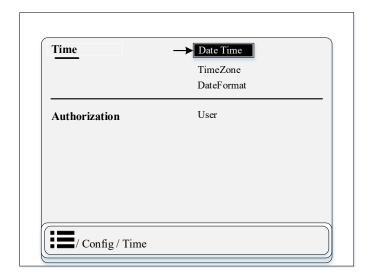

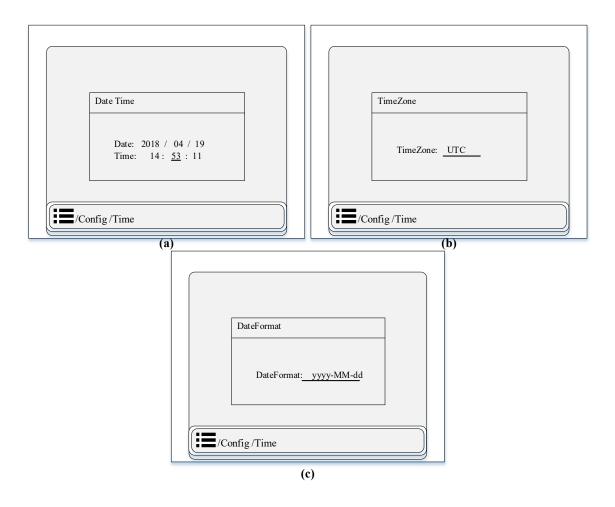

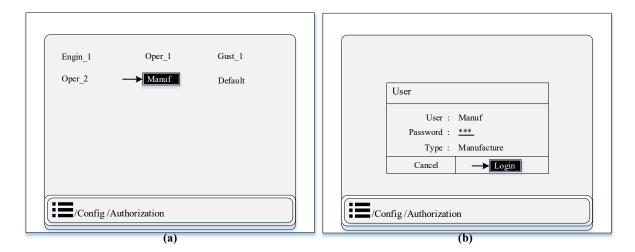

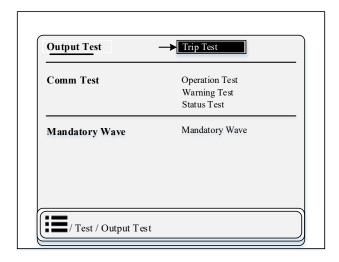

## 2.8.17 Underfrequency Protection